IDT74FCT88915TT55

Overview

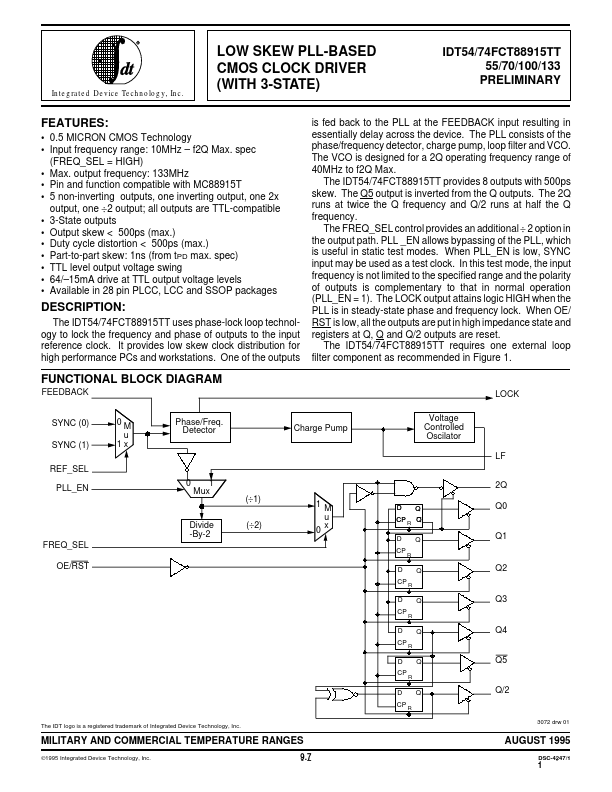

The IDT54/74FCT88915TT uses phase-lock loop technology to lock the frequency and phase of outputs to the input reference clock. It provides low skew clock distribution for high performance PCs and workstations.

- 0.5 MICRON CMOS Technology

- Input frequency range: 10MHz - f2Q Max. spec (FREQ_SEL = HIGH)

- Max. output frequency: 133MHz

- Pin and function compatible with MC88915T

- 5 non-inverting outputs, one inverting output, one 2x output, one ÷ 2 output; all outputs are TTL-compatible

- 3-State outputs

- Output skew < 500ps (max.)

- Duty cycle distortion < 500ps (max.)

- Part-to-part skew: 1ns (from tPD max. spec)

- TTL level output voltage swing