IDT74FCT3907

3.3V PENTIUM CLOCK SYNTHESIZER (Integrated Device Technology)

IDT74FCT3244

3.3V CMOS OCTAL BUFFER/LINE DRIVER (Integrated Device Tech)

IDT74FCT3244A

3.3V CMOS OCTAL BUFFER/LINE DRIVER (Integrated Device Tech)

IDT74FCT3245

3.3V CMOS OCTAL BIDIRECTIONAL TRANSCEIVERS (Integrated Device Tech)

IDT74FCT3245

3.3V CMOS OCTAL BIDIRECTIONAL TRANSCEIVER (Renesas)

IDT74FCT3245A

3.3V CMOS OCTAL BIDIRECTIONAL TRANSCEIVERS (Integrated Device Tech)

IDT74FCT3245A

3.3V CMOS OCTAL BIDIRECTIONAL TRANSCEIVER (Renesas)

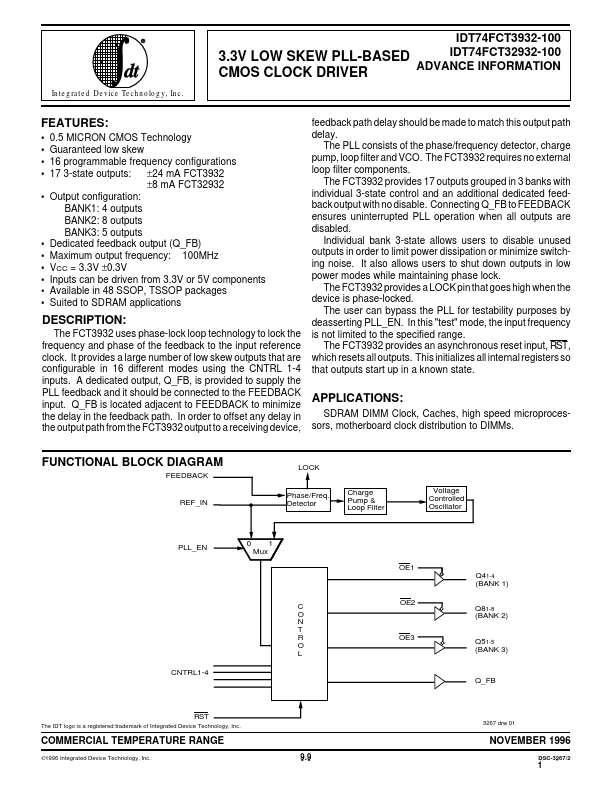

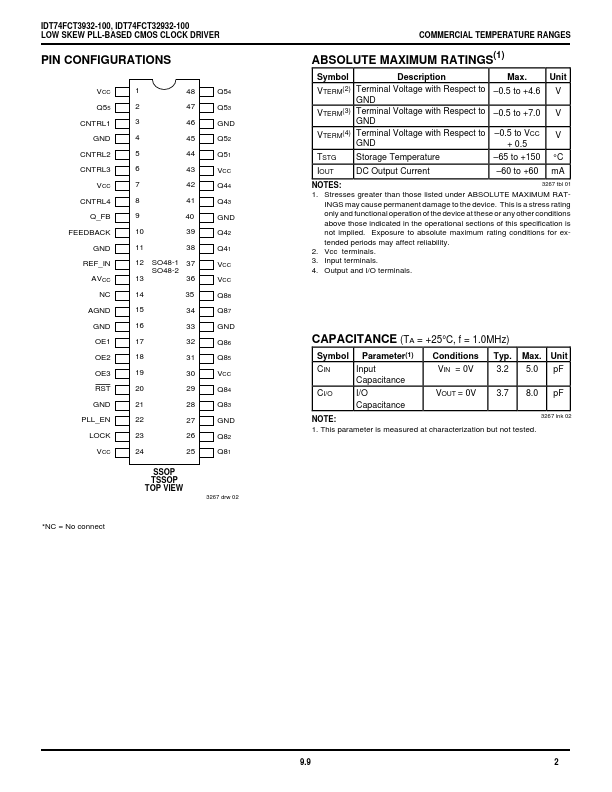

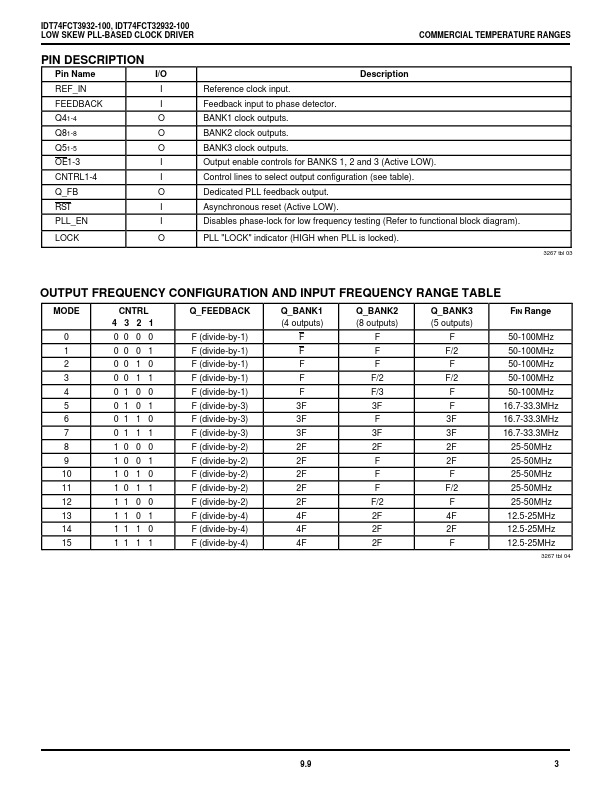

IDT74FCT32932-100

3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER (Integrated Device Tech)

IDT74FCT3573

3.3V CMOS OCTAL TRANSPARENT LATCHES (Integrated Device Tech)

IDT74FCT3573A

3.3V CMOS OCTAL TRANSPARENT LATCHES (Integrated Device Tech)