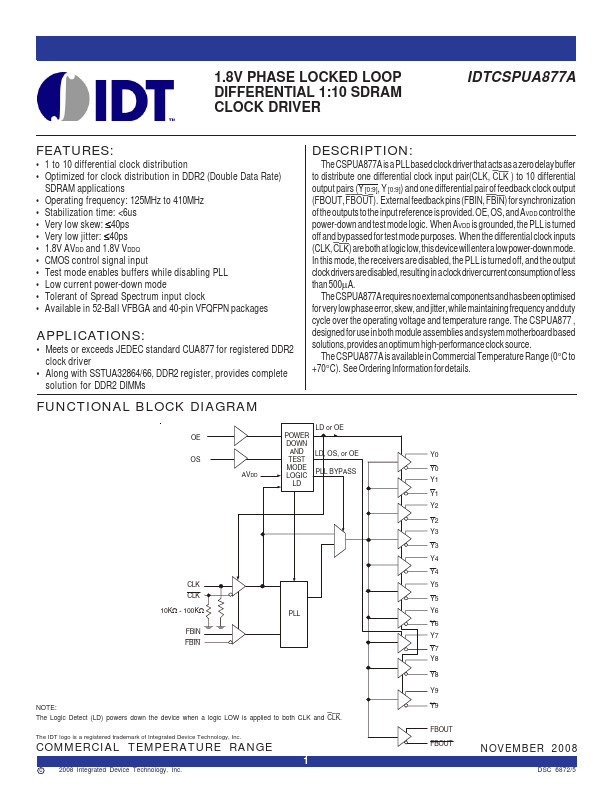

IDTCSPUA877A Description

IDTCSPUA877A 1 to 10 differential clock distribution Optimized for clock distribution in DDR2 (Double Data Rate) SDRAM applications Operating frequency: 125MHz to 410MHz Stabilization time: ≤40ps 1.8V AVDD and 1.8V VDDQ CMOS control signal input Test mode enables buffers while disabling PLL Low current power-down mode Tolerant of Spread Spectrum input clock Available in 52-Ball VFBGA and 40-pin VFQFPN packages...

IDTCSPUA877A Key Features

- 1 to 10 differential clock distribution

- Optimized for clock distribution in DDR2 (Double Data Rate) SDRAM

IDTCSPUA877A Applications

- Operating frequency: 125MHz to 410MHz