QS5917T

Overview

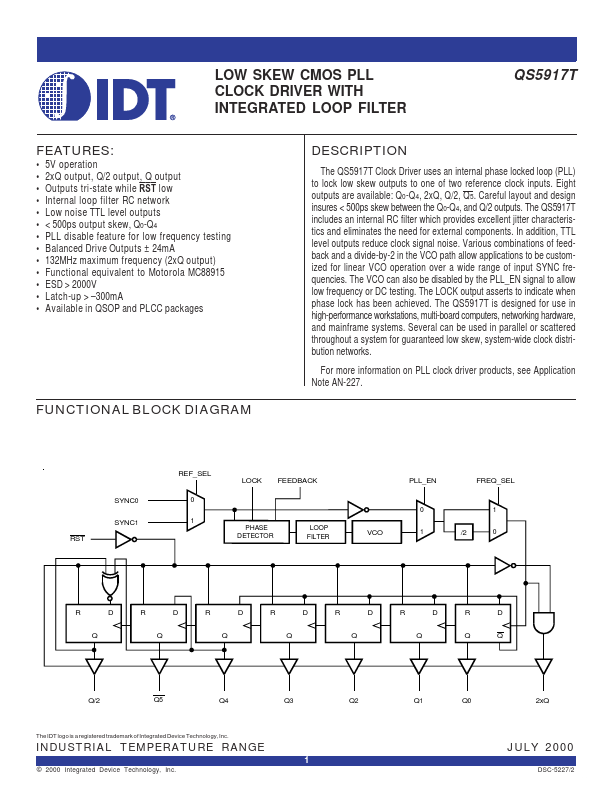

The QS5917T Clock Driver uses an internal phase locked loop (PLL) to lock low skew outputs to one of two reference clock inputs. Eight outputs are available: Q0-Q4, 2xQ, Q/2, Q5.

- QS5917T 5V operation 2xQ output, Q/2 output, Q output Outputs tri-state while RST low Internal loop filter RC network Low noise TTL level outputs < 500ps output skew, Q0-Q4 PLL disable feature for low frequency testing Balanced Drive Outputs ± 24mA 132MHz maximum frequency (2xQ output) Functional equivalent to Motorola MC88915 ESD > 2000V Latch-up > -300mA Available in QSOP and PLCC packages