QS5LV91955J

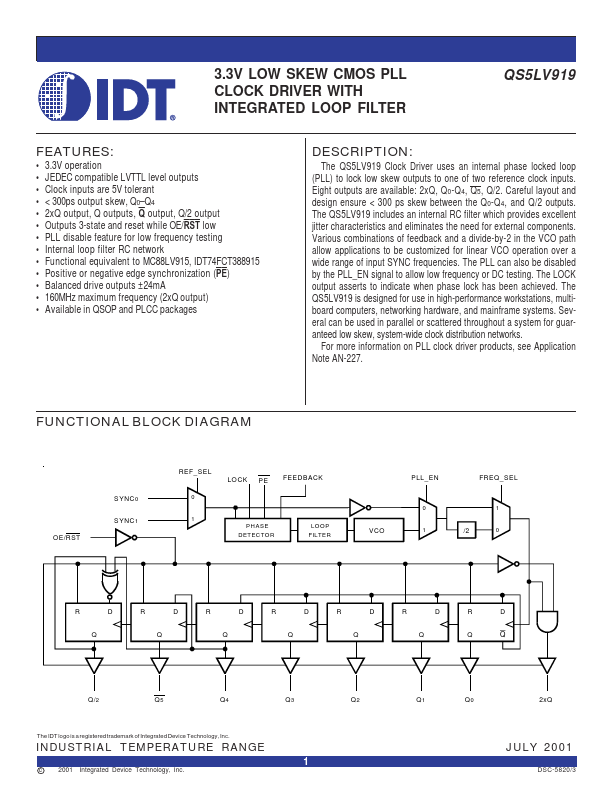

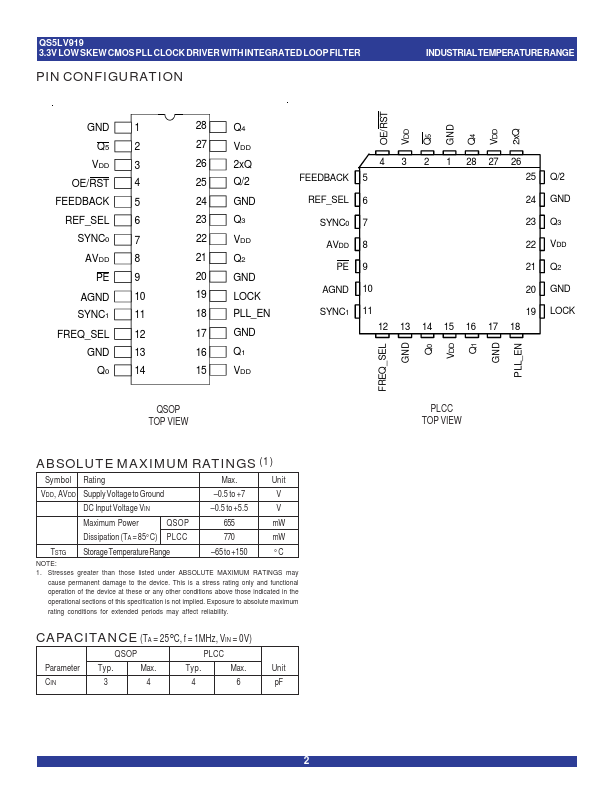

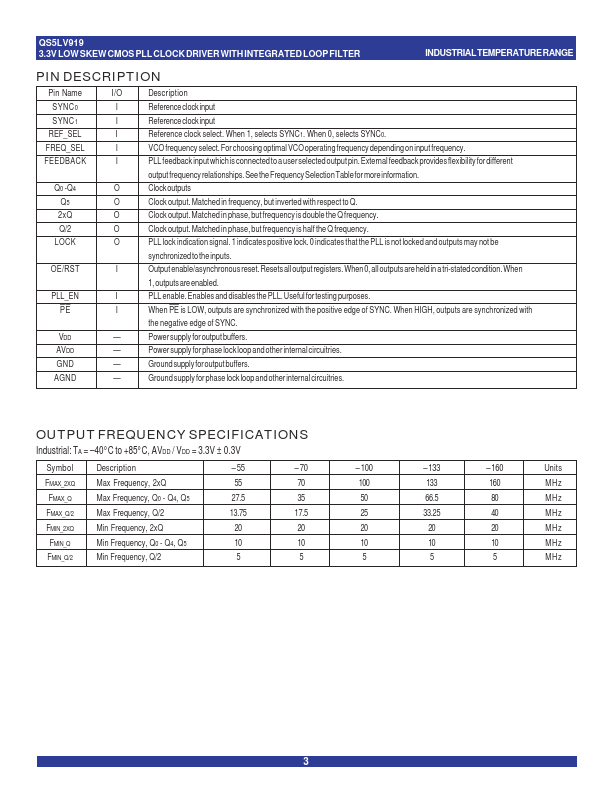

3.3V LOW SKEW CMOS PLL CLOCK DRIVER (Integrated Device Technology)

QS5LV919133Q

3.3V LOW SKEW CMOS PLL CLOCK DRIVER (Integrated Device Technology)

QS5LV919160J

3.3V LOW SKEW CMOS PLL CLOCK DRIVER (Integrated Device Technology)

QS5LV919160Q

3.3V LOW SKEW CMOS PLL CLOCK DRIVER (Integrated Device Technology)

QS5LV91970J

3.3V LOW SKEW CMOS PLL CLOCK DRIVER (Integrated Device Technology)

QS5LV91970Q

3.3V LOW SKEW CMOS PLL CLOCK DRIVER (Integrated Device Technology)

QS5100

Digital FX LSI (Altonics)

QS518

Solder Profile and Stencil Design (Spreadtrum)

QS5244

Low Skew CMOS 8 Bit Buffer / Line Drivers (Quality)

QS532805

GUARANTEED LOW SKEW 3.3V CMOS CLOCK DRIVER/BUFFER (Integrated Device Technology)