QS5LV91955J

QS5LV91955J is 3.3V LOW SKEW CMOS PLL CLOCK DRIVER manufactured by Integrated Device Technology.

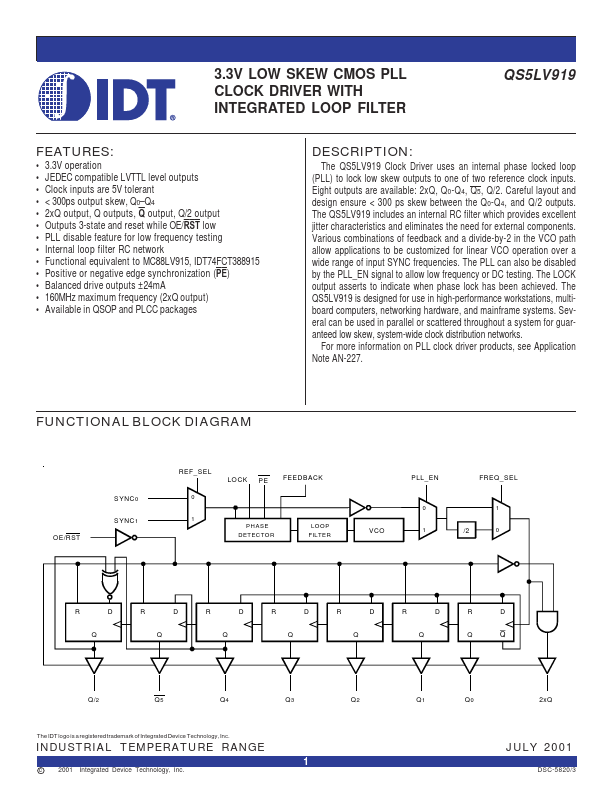

QS5LV919 3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

INDUSTRIAL TEMPERATURE RANGE

3.3V LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

Features

: DESCRIPTION:

QS5LV919

- -

- -

- -

- -

- -

- -

- 3.3V operation JEDEC patible LVTTL level outputs Clock inputs are 5V tolerant < 300ps output skew, Q0- Q4 2xQ output, Q outputs, Q output, Q/2 output Outputs 3-state and reset while OE/RST low PLL disable feature for low frequency testing Internal loop filter RC network Functional equivalent to MC88LV915, IDT74FCT388915 Positive or negative edge synchronization (PE) Balanced drive outputs ±24mA 160MHz maximum frequency (2xQ output) Available in QSOP and PLCC...