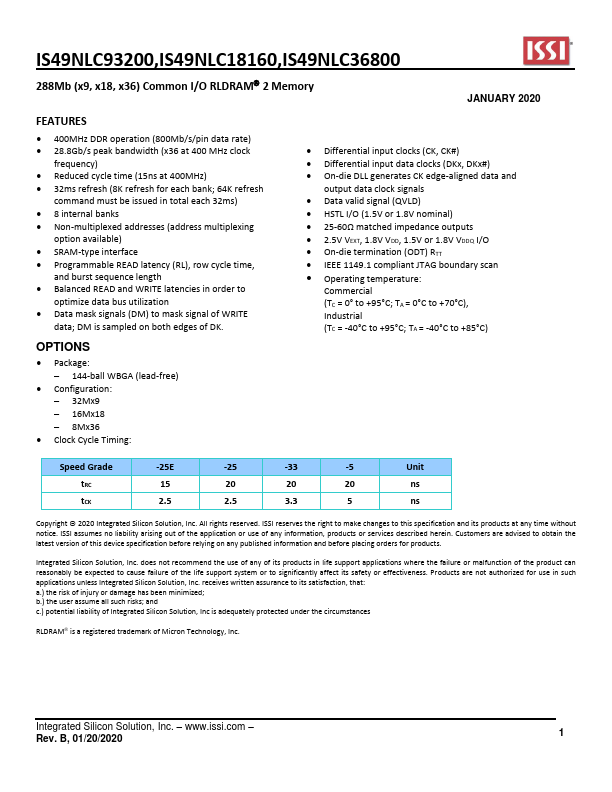

IS49NLC93200

Key Features

- 400MHz DDR operation (800Mb/s/pin data rate)

- 28.8Gb/s peak bandwidth (x36 at 400 MHz clock frequency)

- Reduced cycle time (15ns at 400MHz)

- 32ms refresh (8K refresh for each bank; 64K refresh command must be issued in total each 32ms)

- 8 internal banks

- Non-multiplexed addresses (address multiplexing option available)

- SRAM-type interface

- Programmable READ latency (RL), row cycle time, and burst sequence length

- Balanced READ and WRITE latencies in order to optimize data bus utilization

- Data mask signals (DM) to mask signal of WRITE data; DM is sampled on both edges of DK. OPTIONS