DS34S101 Overview

Key Specifications

Height: 10 mm

Length: 10 mm

Max Operating Temp: 85 °C

Min Operating Temp: -40 °C

Description

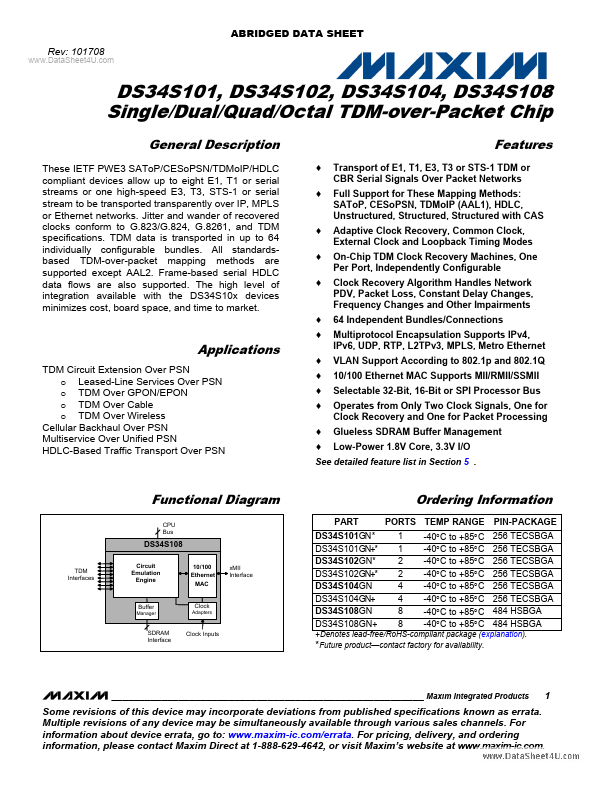

These IETF PWE3 SAToP/CESoPSN/TDMoIP/HDLC compliant devices allow up to eight E1, T1 or serial streams or one high-speed E3, T3, STS-1 or serial stream to be transported transparently over IP, MPLS or Ethernet networks. Jitter and wander of recovered clocks conform to G.823/G.824, G.8261, and TDM specifications.