MAX3674

Key Features

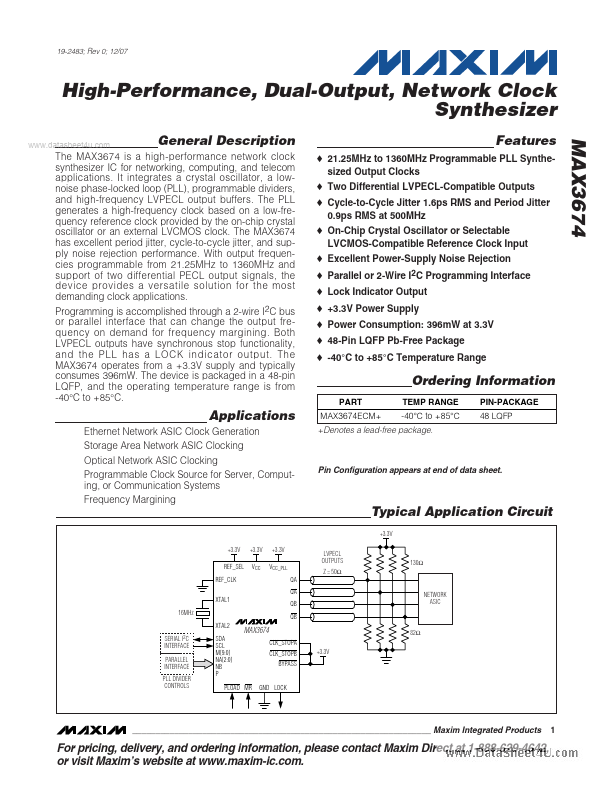

- 21.25MHz to 1360MHz Programmable PLL Synthesized Output Clocks

- Two Differential LVPECL-compatible Outputs

- Cycle-to-Cycle Jitter 1.6ps RMS and Period Jitter 0.9ps RMS at 500MHz

- On-Chip Crystal Oscillator or Selectable LVCMOS-compatible Reference Clock Input

- Excellent Power-Supply Noise Rejection

- Parallel or 2-Wire I2C Programming Interface

- Lock Indicator Output

- +3.3V Power Supply

- Power Consumption: 396mW at 3.3V

- 48-Pin LQFP Pb-Free Package