SY10E195 Description

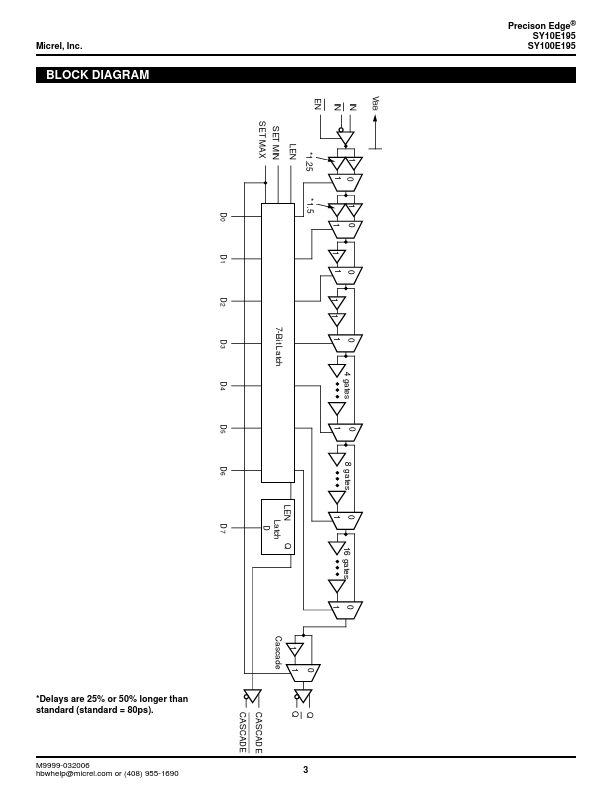

The SY10/100E195 are programmable delay chips (PDCs) designed primarily for clock de-skewing and timing adjustment. They provide variable delay of a differential ECL input transition. The delay section consists of a chain of gates organized as shown in the logic diagram.