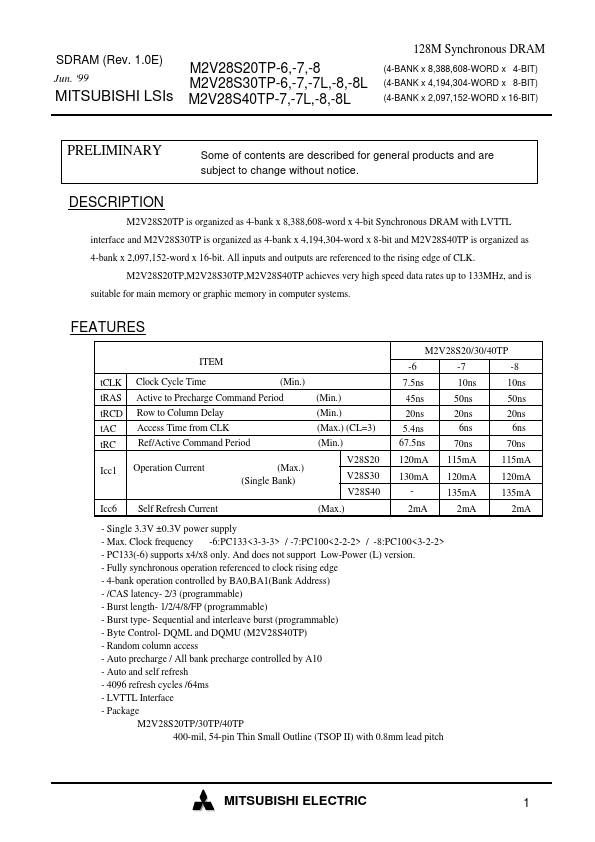

M2V28S30TP Overview

Key Specifications

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 3 V

Max Frequency: 100 MHz

Description

M2V28S20TP is organized as 4-bank x 8,388,608-word x 4-bit Synchronous DRAM with LVTTL interface and M2V28S30TP is organized as 4-bank x 4,194,304-word x 8-bit and M2V28S40TP is organized as 4-bank x 2,097,152-word x 16-bit. All inputs and outputs are referenced to the rising edge of CLK.

Key Features

- Single 3.3V ±0.3V power supply

- PC133(-6) supports x4/x8 only. And does not support Low-Power (L) version

- Fully synchronous operation referenced to clock rising edge

- 4-bank operation controlled by BA0,BA1(Bank Address)

- /CAS latency- 2/3 (programmable)