Datasheet Summary

..

Century Semiconductor Inc.

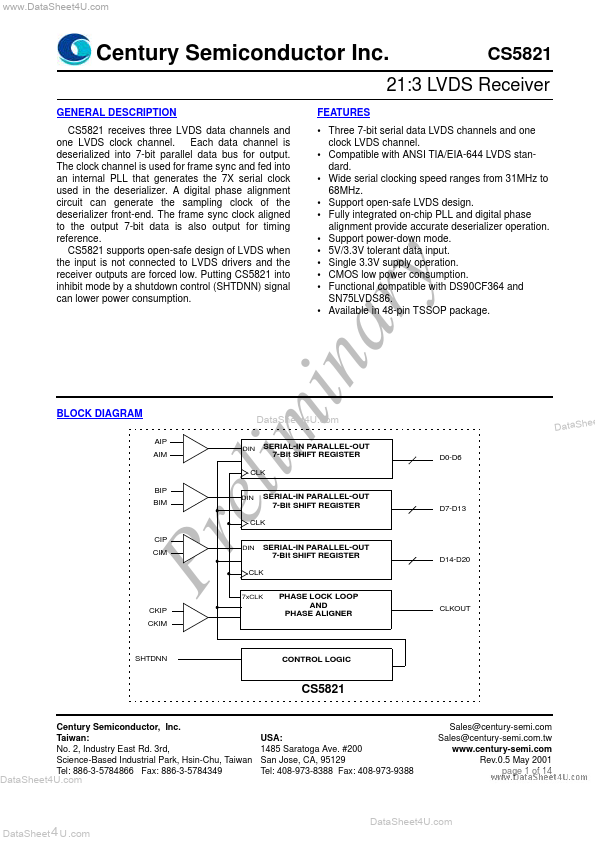

GENERAL DESCRIPTION CS5821 receives three LVDS data channels and one LVDS clock channel. Each data channel is deserialized into 7-bit parallel data bus for output. The clock channel is used for frame sync and fed into an internal PLL that generates the 7X serial clock used in the deserializer. A digital phase alignment circuit can generate the sampling clock of the deserializer front-end. The frame sync clock aligned to the output 7-bit data is also output for timing reference. CS5821 supports open-safe design of LVDS when the input is not connected to LVDS drivers and the receiver outputs are forced low. Putting CS5821 into inhibit mode by a...