NE24200

Overview

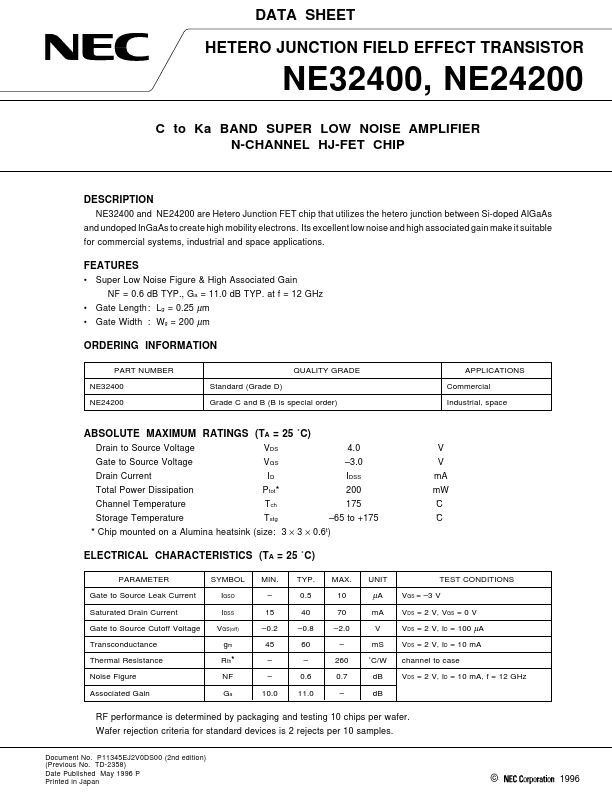

NE32400 and NE24200 are Hetero Junction FET chip that utilizes the hetero junction between Si-doped AlGaAs and undoped InGaAs to create high mobility electrons. Its excellent low noise and high associated gain make it suitable for commercial systems, industrial and space applications.

- Super Low Noise Figure & High Associated Gain NF = 0.6 dB TYP., Ga = 11.0 dB TYP. at f = 12 GHz

- Gate Length : Lg = 0.25 µm

- Gate Width : Wg = 200 µm