UPD4481161

UPD4481161 is 8M-BIT ZEROSB SRAM manufactured by NEC.

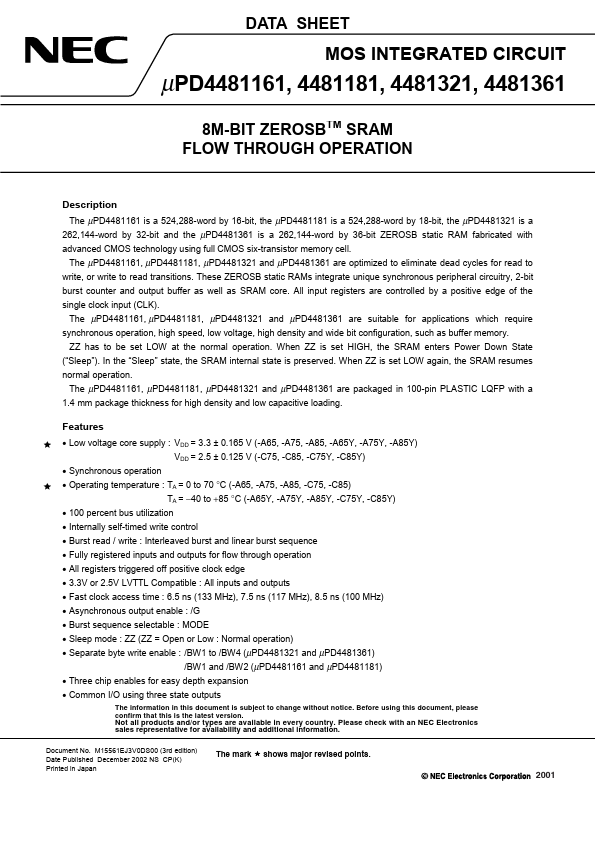

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD4481161, 4481181, 4481321, 4481361

8M-BIT ZEROSBTM SRAM FLOW THROUGH OPERATION

Description

The µPD4481161 is a 524,288-word by 16-bit, the µPD4481181 is a 524,288-word by 18-bit, the µPD4481321 is a 262,144-word by 32-bit and the µPD4481361 is a 262,144-word by 36-bit ZEROSB static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell. The µPD4481161, µPD4481181, µPD4481321 and µPD4481361 are optimized to eliminate dead cycles for read to write, or write to read transitions. These ZEROSB static RAMs integrate unique synchronous peripheral circuitry, 2-bit burst counter and output buffer as well as SRAM core. All...