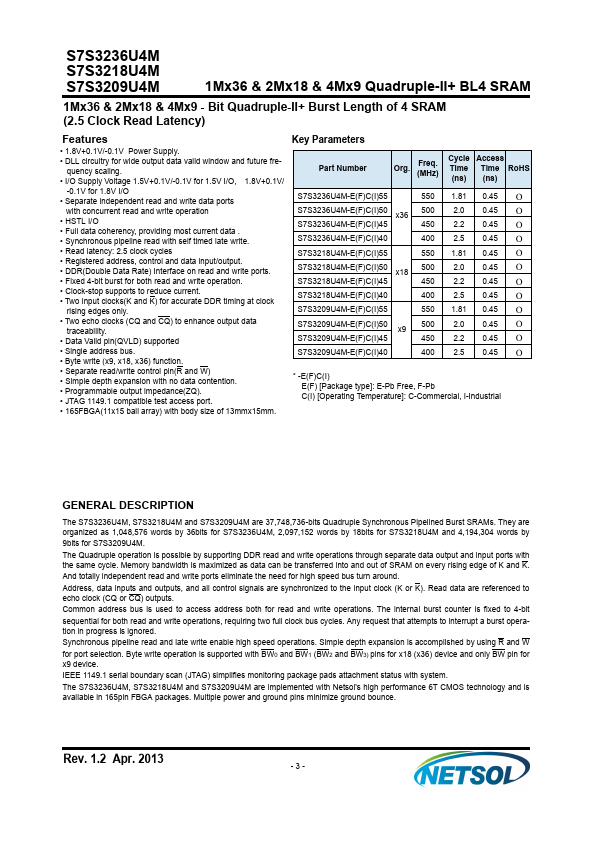

S7S3209U4M Description

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IN NETSOL PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND. For updates or additional information about Netsol products, contact your nearest Netsol office.

S7S3209U4M Key Features

- 1.8V+0.1V/-0.1V Power Supply

- DLL circuitry for wide output data valid window and future fre

- I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O, 1.8V+0.1V/

- 0.1V for 1.8V I/O

- Separate independent read and write data ports

- HSTL I/O

- Full data coherency, providing most current data

- Synchronous pipeline read with self timed late write

- Read latency: 2.5 clock cycles

- Registered address, control and data input/output

S7S3209U4M Applications

- Netsol reserves the rights to change products or specification without notice