Datasheet Summary

..

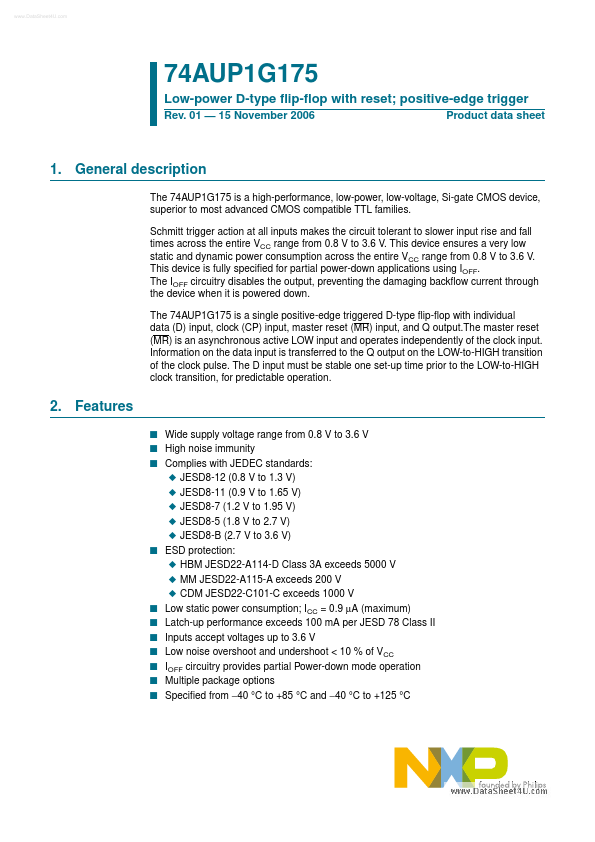

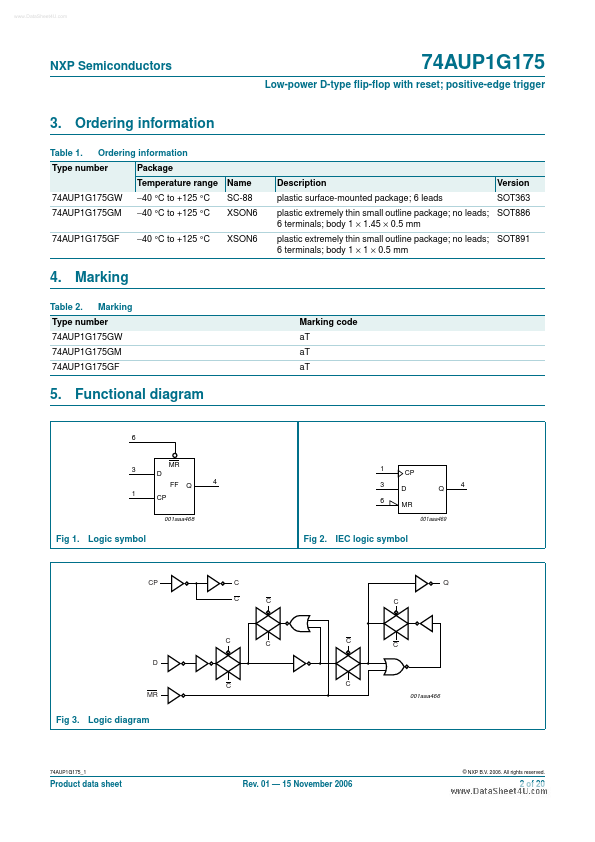

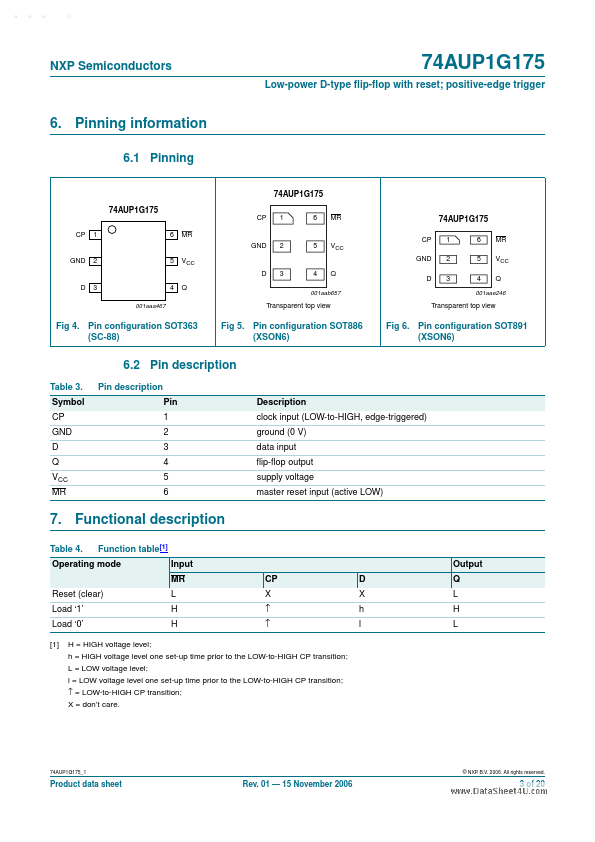

Low-power D-type flip-flop with reset; positive-edge trigger

Rev. 01

- 15 November 2006 Product data sheet

1. General description

The 74AUP1G175 is a high-performance, low-power, low-voltage, Si-gate CMOS device, superior to most advanced CMOS patible TTL families. Schmitt trigger action at all inputs makes the circuit tolerant to slower input rise and fall times across the entire VCC range from 0.8 V to 3.6 V. This device ensures a very low static and dynamic power consumption across the entire VCC range from 0.8 V to 3.6 V. This device is fully specified for partial power-down applications using IOFF. The IOFF circuitry disables the output, preventing the...