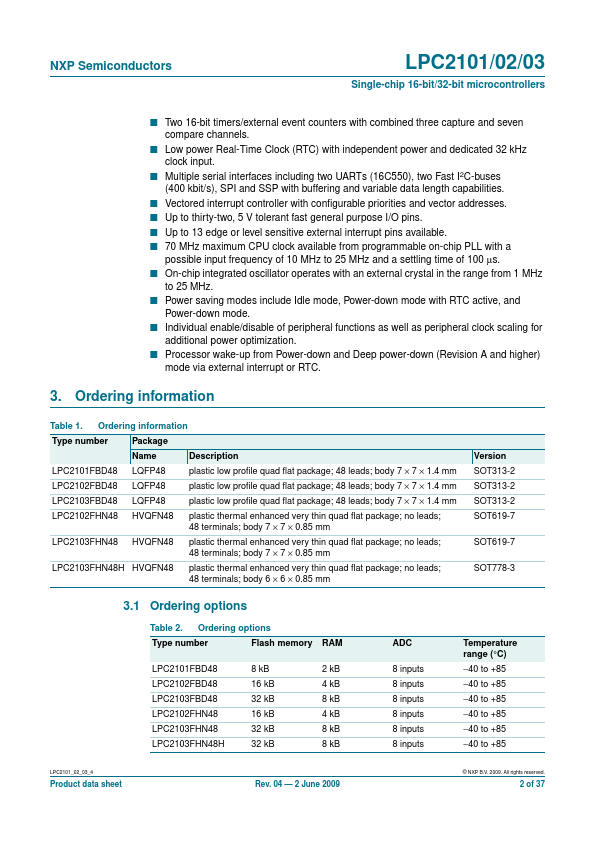

LPC2102 Overview

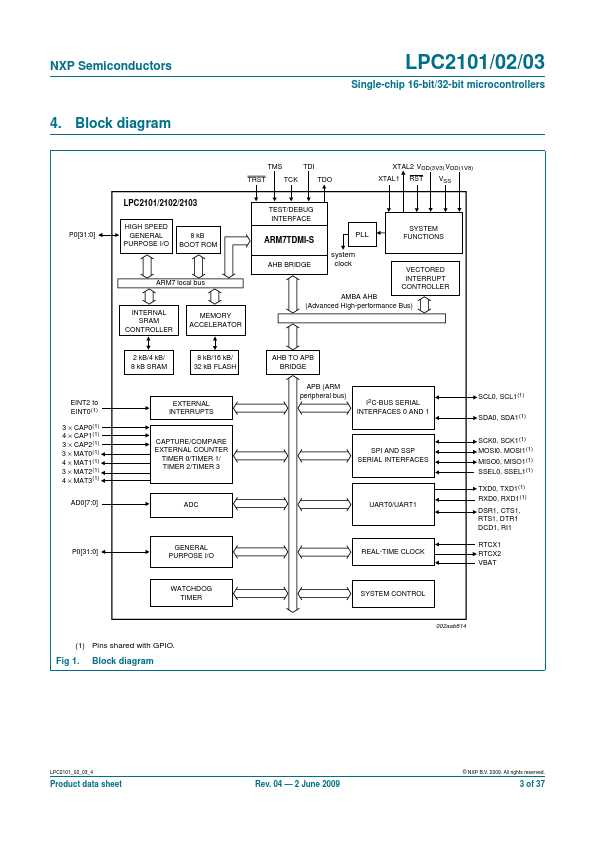

The LPC2101/02/03 microcontrollers are based on a 16-bit/32-bit ARM7TDMI-S CPU with real-time emulation that bines the microcontroller with 8 kB, 16 kB or 32 kB of embedded high-speed flash memory. A 128-bit wide memory interface and a unique accelerator architecture enable 32-bit code execution at the maximum clock rate. For critical performance in interrupt service routines and DSP algorithms, this increases...