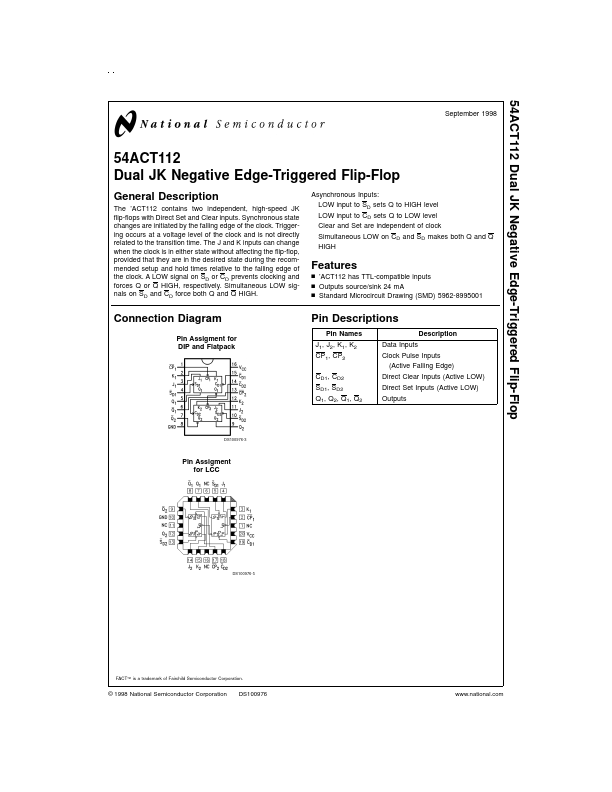

| Part | 54ACT112 |

|---|---|

| Description | Dual JK Negative Edge-Triggered Flip-Flop |

| Manufacturer | National Semiconductor |

| Size | 158.57 KB |

Pricing from 127.15 USD, available from Rochester Electronics and DigiKey Marketplace.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 268 | 1+ : 127.15 USD 25+ : 123.34 USD 100+ : 119.52 USD 500+ : 115.71 USD |

View Offer |

| DigiKey Marketplace | 268 | 2+ : 158.94 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 54ACT11241 | Texas Instruments | OCTAL BUFFERS/LINE DRIVERS |

| 54ACT11280 | Texas Instruments | 9-BIT PARITY GENERATORS/CHECKERS |

| 54ACT11253 | Texas Instruments | DUAL 1-OF-4 DATA SELECTORS/MULTIPLEXERS |

| 54ACT11034 | Texas Instruments | Hex Noninverters |

| 54ACT11520 | Texas Instruments | 8-Bit Identity Comparators |