Overview

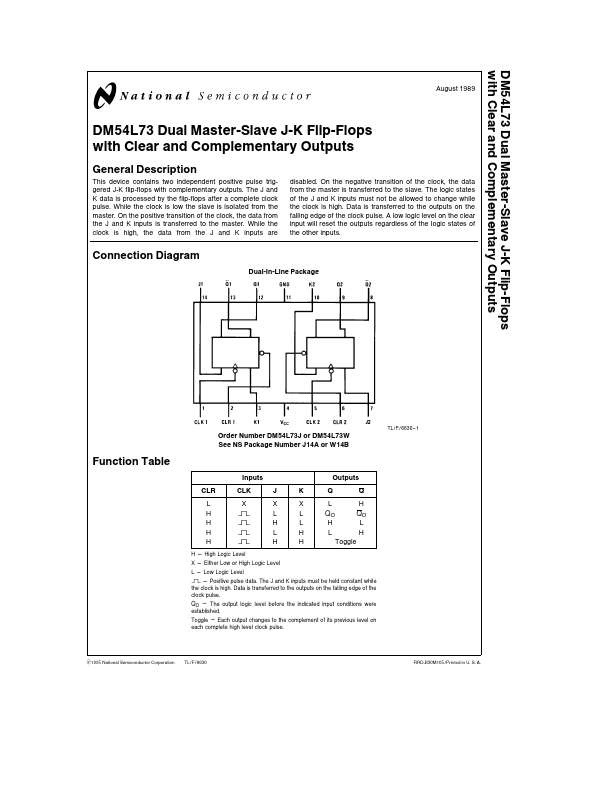

This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs The J and K data is processed by the flip-flops after a complete clock pulse While the clock is low the slave is isolated from the master On the positive transition of the clock the data from the J and K inputs is transferred to the master While the clock is high the data from the J and K inputs are disabled On the negative transition of the clock the data from the master is transferred to the slave The logic states of the J and K inputs must not be allowed to change while the clock is high Data is transferred to the outputs on the falling edge of the clock pulse A low logic level on the clear input will reset the outputs regardless of the logic states of the other inputs Connection Diagram Dual-In-Line Package TL F 6630 - 1 Order Number DM54L73J or DM54L73W See NS Package Number J14A or W14B Function.