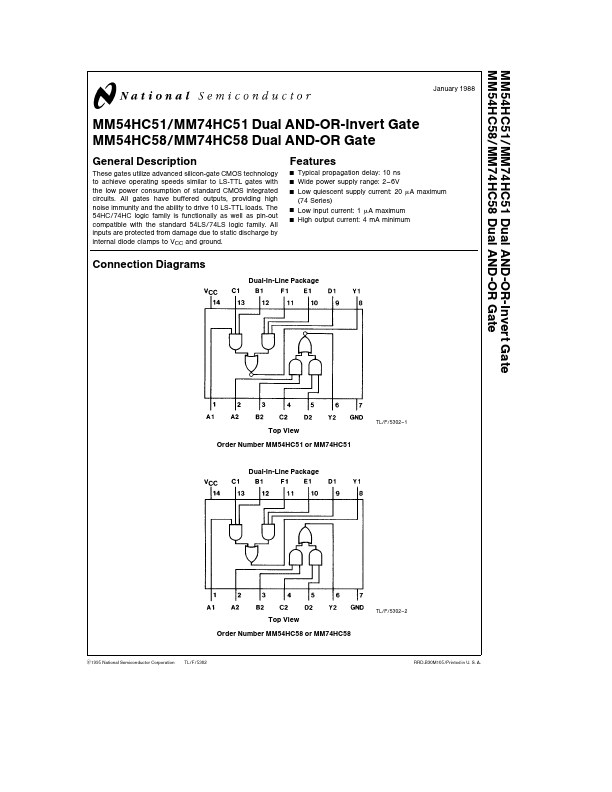

MM74HC51 Overview

Key Specifications

Package: SOP

Operating Voltage: 5 V

Max Voltage (typical range): 6 V

Min Voltage (typical range): 2 V

Description

These gates utilize advanced silicon-gate CMOS technology to achieve operating speeds similar to LS-TTL gates with the low power consumption of standard CMOS integrated circuits All gates have buffered outputs providing high noise immunity and the ability to drive 10 LS-TTL loads The 54HC 74HC logic family is functionally as well as pin-out compatible with the standard 54LS 74LS logic family All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.