NB4L16M Overview

Key Specifications

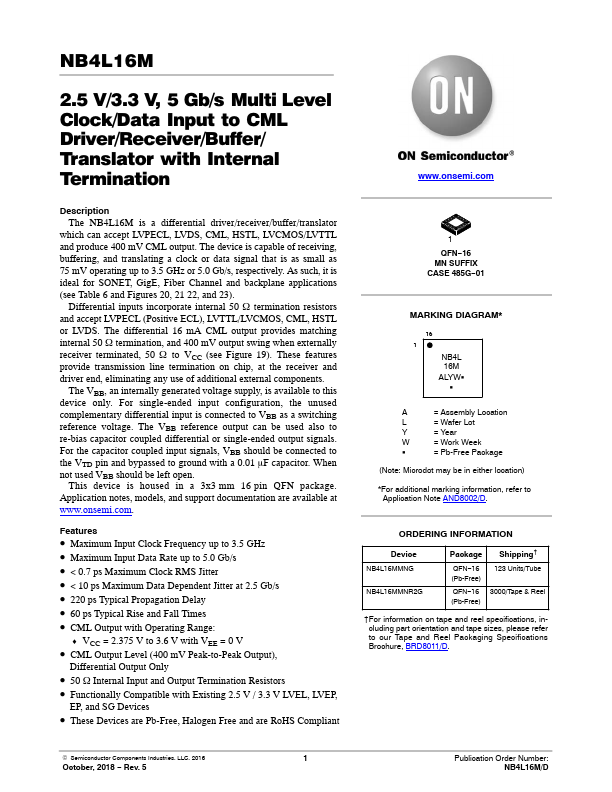

Package: QFN

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 2.5 V

Description

The NB4L16M is a differential driver/receiver/buffer/translator which can accept LVPECL, LVDS, CML, HSTL, LVCMOS/LVTTL and produce 400 mV CML output. The device is capable of receiving, buffering, and translating a clock or data signal that is as small as 75 mV operating up to 3.5 GHz or 5.0 Gb/s, respectively.

Key Features

- Maximum Input Clock Frequency up to 3.5 GHz

- Maximum Input Data Rate up to 5.0 Gb/s

- < 0.7 ps Maximum Clock RMS Jitter

- < 10 ps Maximum Data Dependent Jitter at 2.5 Gb/s

- 220 ps Typical Propagation Delay