NB4N855S Key Features

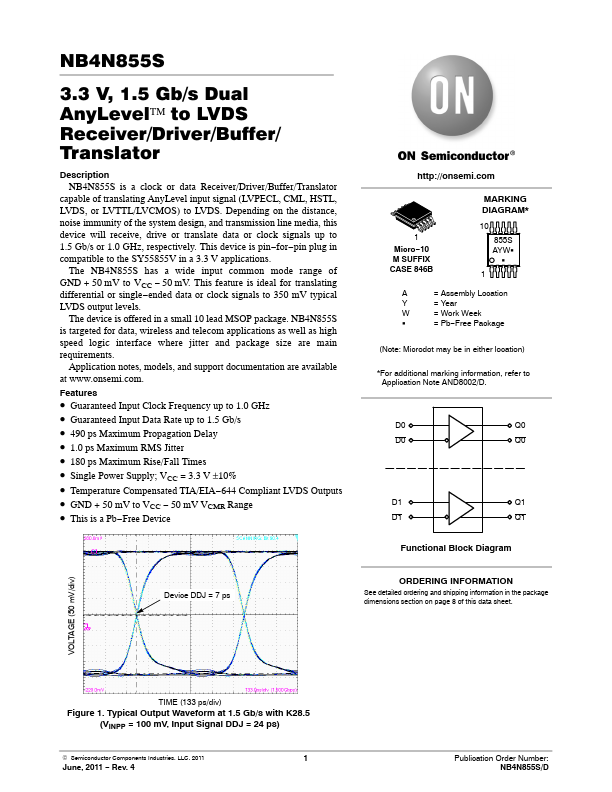

- Guaranteed Input Clock Frequency up to 1.0 GHz

- Guaranteed Input Data Rate up to 1.5 Gb/s

- 490 ps Maximum Propagation Delay

- 1.0 ps Maximum RMS Jitter

- 180 ps Maximum Rise/Fall Times

- Single Power Supply; VCC = 3.3 V ±10%

- Temperature pensated TIA/EIA-644 pliant LVDS Outputs

- GND + 50 mV to VCC

- 50 mV VCMR Range

- This is a Pb-Free Device