NB4N11M

NB4N11M is Multi Level Clock/Data Input to CML Receiver/Buffer/Translator manufactured by onsemi.

3.3 V, 2.5 Gb/s Multi Level Clock/Data Input to CML Receiver/Buffer/Translator

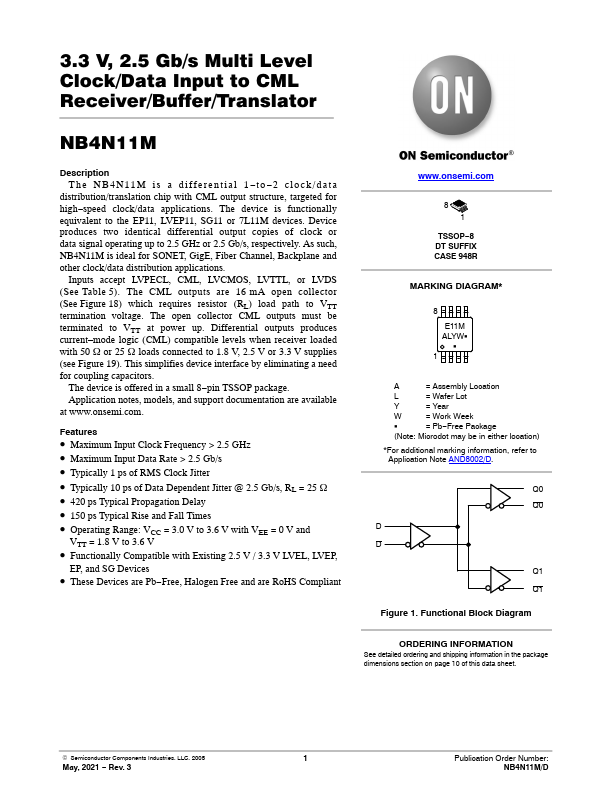

Description The NB4N11M is a differential 1- to- 2 clock/data distribution/translation chip with CML output structure, targeted for high- speed clock/data applications. The device is functionally equivalent to the EP11, LVEP11, SG11 or 7L11M devices. Device produces two identical differential output copies of clock or data signal operating up to 2.5 GHz or 2.5 Gb/s, respectively. As such, NB4N11M is ideal for SONET, GigE, Fiber Channel, Backplane and other clock/data distribution applications.

Inputs accept LVPECL, CML, LVCMOS, LVTTL, or LVDS (See Table 5). The CML outputs are 16 mA open collector (See...