NB4N111K

NB4N111K is Clock Fanout Buffer manufactured by onsemi.

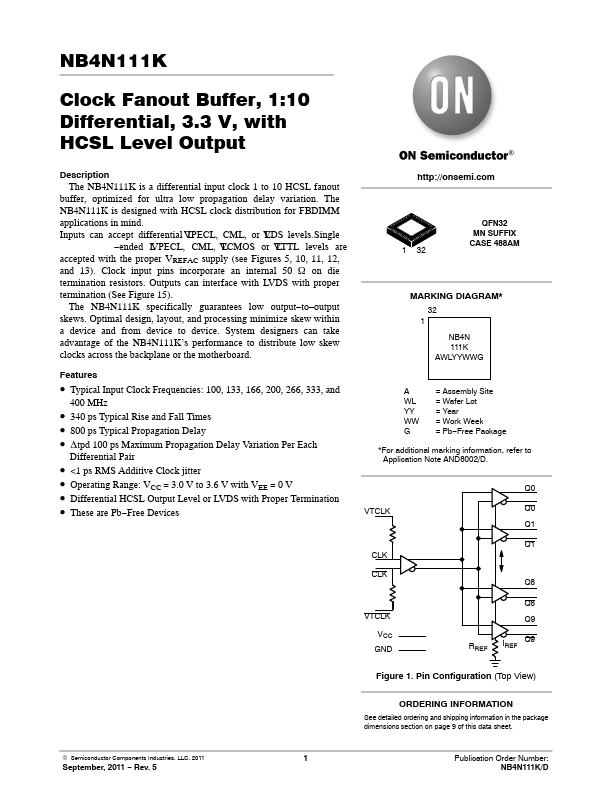

Clock Fanout Buffer, 1:10 Differential, 3.3 V, with HCSL Level Output

Description The NB4N111K is a differential input clock 1 to 10 HCSL fanout buffer, optimized for ultra low propagation delay variation. The NB4N111K is designed with HCSL clock distribution for FBDIMM applications in mind. Inputs can accept differential VLPECL, CML, or VLDS levels.Single

- ended LVPECL, CML, VLCMOS or VLTTL levels are accepted with the proper VREFAC supply (see Figures 5, 10, 11, 12, and 13). Clock input pins incorporate an internal 50 W on die termination resistors. Outputs can interface with LVDS with proper termination (See Figure 15).

The NB4N111K specifically guarantees low output- to-...