NB4N11S

NB4N11S is 3.3V 1:2 AnyLevel Input to LVDS Fanout Buffer /Translator manufactured by onsemi.

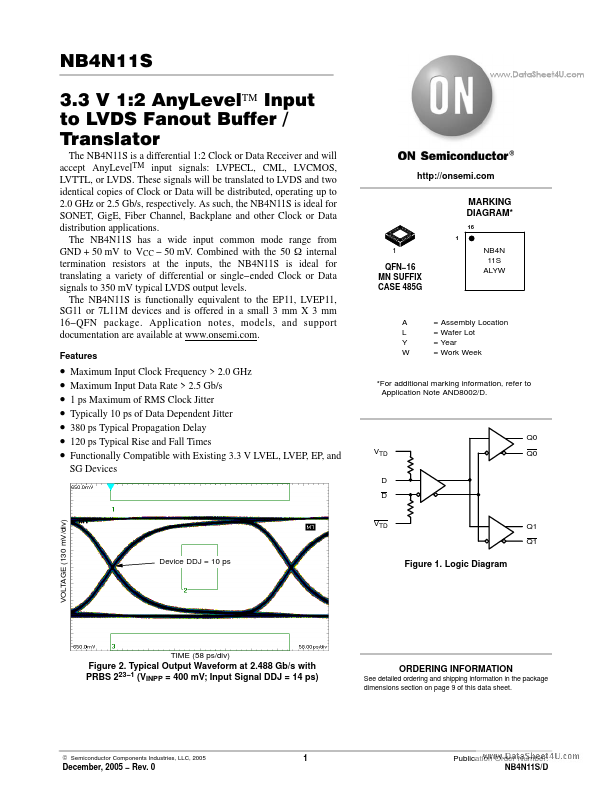

NB4N11S 3.3 V 1:2 AnyLevel™ Input to LVDS Fanout Buffer / Translator

The NB4N11S is a differential 1:2 Clock or Data Receiver and will accept AnyLevelTM input signals: LVPECL, CML, LVCMOS, LVTTL, or LVDS. These signals will be translated to LVDS and two identical copies of Clock or Data will be distributed, operating up to 2.0 GHz or 2.5 Gb/s, respectively. As such, the NB4N11S is ideal for SONET, GigE, Fiber Channel, Backplane and other Clock or Data distribution applications. The NB4N11S has a wide input mon mode range from GND + 50 mV to VCC

- 50 mV. bined with the 50 W internal termination resistors at the inputs, the NB4N11S is ideal for translating a variety of differential or...