NB7V33M

Description

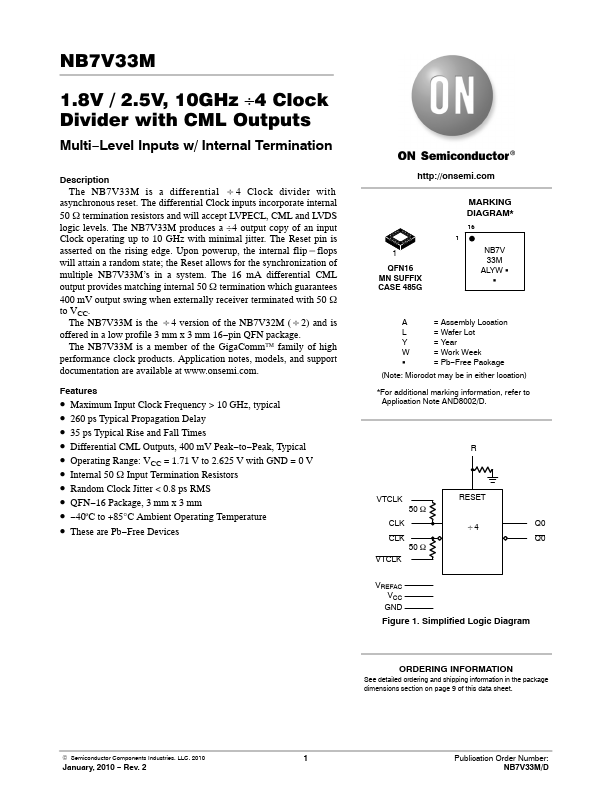

The NB7V33M is a differential B4 Clock divider with asynchronous reset. The differential Clock inputs incorporate internal 50 W termination resistors and will accept LVPECL, CML and LVDS logic levels.

Key Features

- Maximum Input Clock Frequency > 10 GHz, typical

- 260 ps Typical Propagation Delay

- 35 ps Typical Rise and Fall Times

- Differential CML Outputs, 400 mV Peak-to-Peak, Typical

- Operating Range: VCC = 1.71 V to 2.625 V with GND = 0 V

- Internal 50 W Input Termination Resistors

- Random Clock Jitter < 0.8 ps RMS

- QFN-16 Package, 3 mm x 3 mm

- 40ºC to +85°C Ambient Operating Temperature

- Simplified Logic Diagram