PLL601-15

PLL601-15 is Low Phase Noise PLL Clock Multiplier manufactured by PhaseLink.

m o .c U 4 t e Features e h

- Full swing CMOS S outputs with 25 mA drive capability a at TTL levels. t 20-30MHz crystal or clock.

- Reference a

- Integrated crystal load capacitor: no external .D load capacitor required. w

- Output clocks up to 150MHz at 3.3V. w

- Low phase noise (-126dBc/Hz @ 1kHz). w- Output Enable function.

- -

- -

Preliminary

Low Phase Noise PLL Clock Multiplier

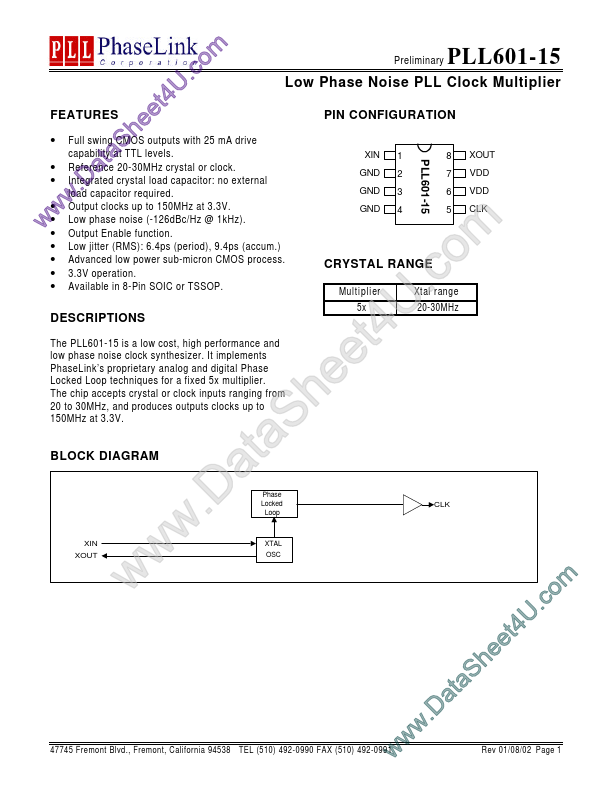

PIN CONFIGURATION

XIN GND GND GND

1 2 3 4

8 7 6 5

XOUT VDD VDD CLK

Low jitter (RMS): 6.4ps (period), 9.4ps (accum.) Advanced low power sub-micron CMOS process. 3.3V operation. Available in 8-Pin SOIC or TSSOP.

DESCRIPTIONS

The PLL601-15 is a low cost, high performance and low phase noise...