HD74HC166 Overview

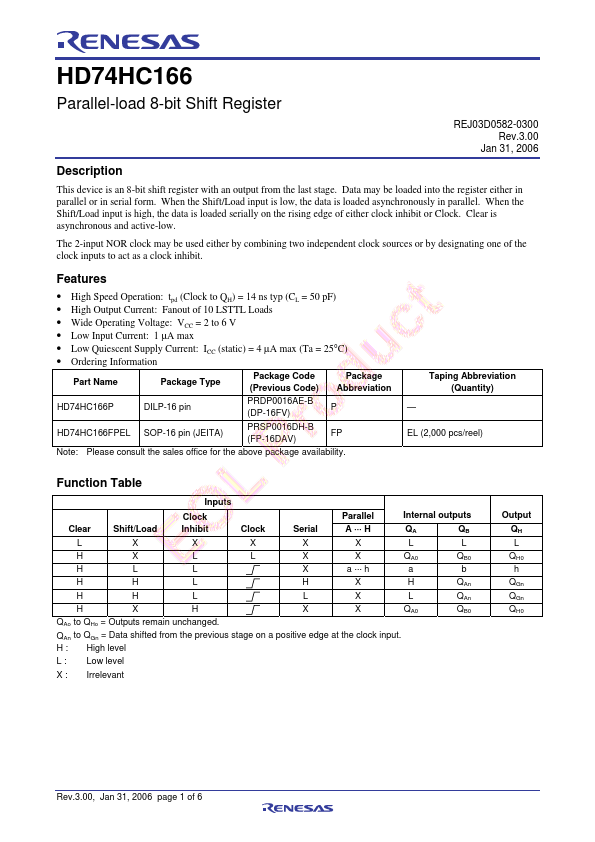

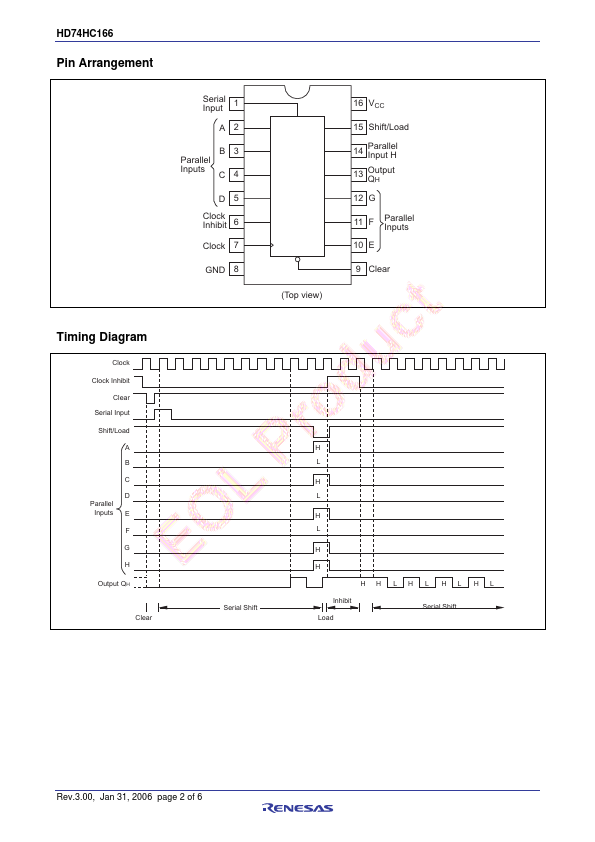

This device is an 8-bit shift register with an output from the last stage. Data may be loaded into the register either in parallel or in serial form. When the Shift/Load input is low, the data is loaded asynchronously in parallel.

HD74HC166 Key Features

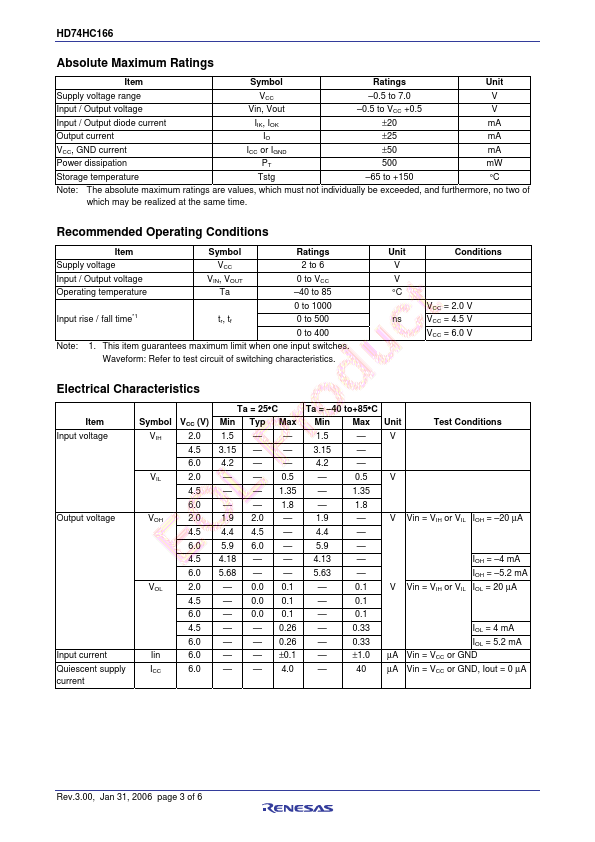

- High Speed Operation: tpd (Clock to QH) = 14 ns typ (CL = 50 pF)

- High Output Current: Fanout of 10 LSTTL Loads

- Wide Operating Voltage: VCC = 2 to 6 V

- Low Input Current: 1 µA max

- Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

- Ordering Information