IDT23S09E

Description

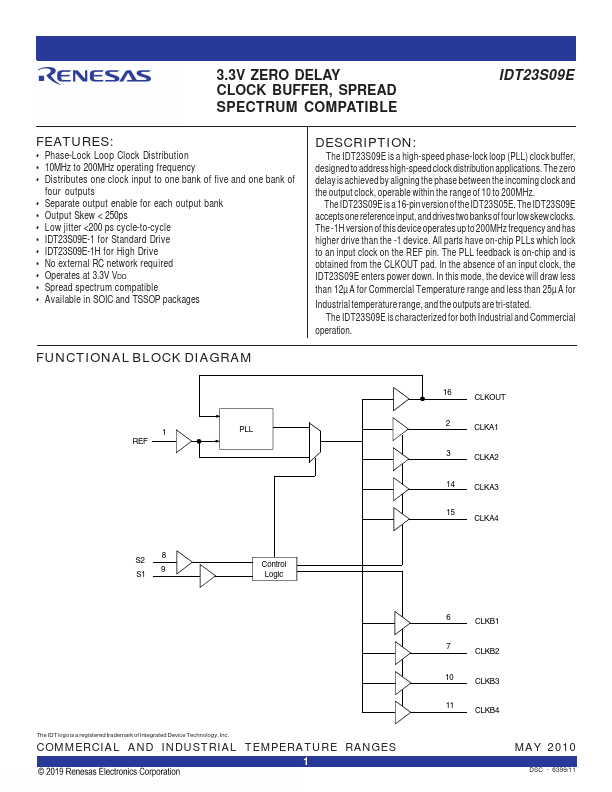

The IDT23S09E is a high-speed phase-lock loop (PLL) clock buffer, designed to address high-speed clock distribution applications.

Key Features

- Phase-Lock Loop Clock Distribution

- 10MHz to 200MHz operating frequency

- Distributes one clock input to one bank of five and one bank of four outputs

- Separate output enable for each output bank

- Output Skew < 250ps

- Low jitter <200 ps cycle-to-cycle

- IDT23S09E-1 for Standard Drive

- IDT23S09E-1H for High Drive

- No external RC network required

- Operates at 3.3V VDD