Datasheet Summary

..

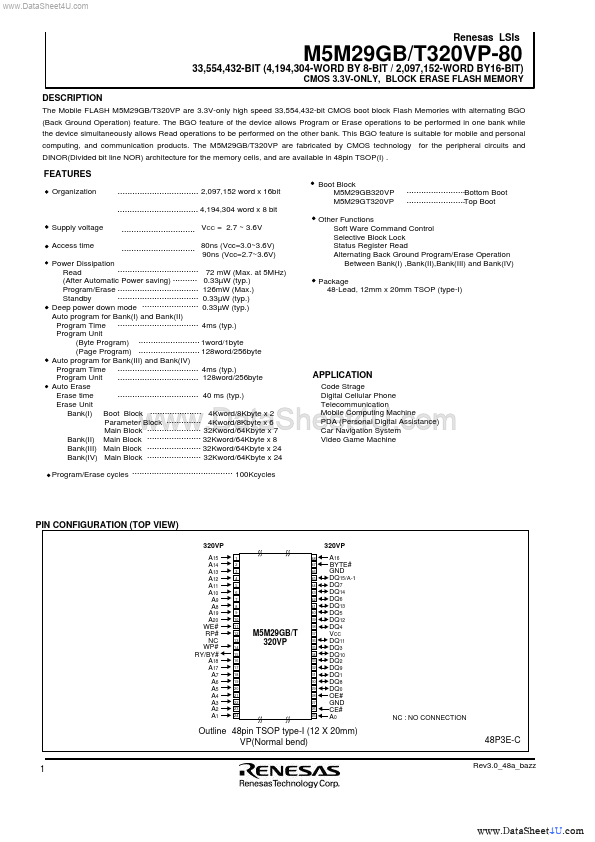

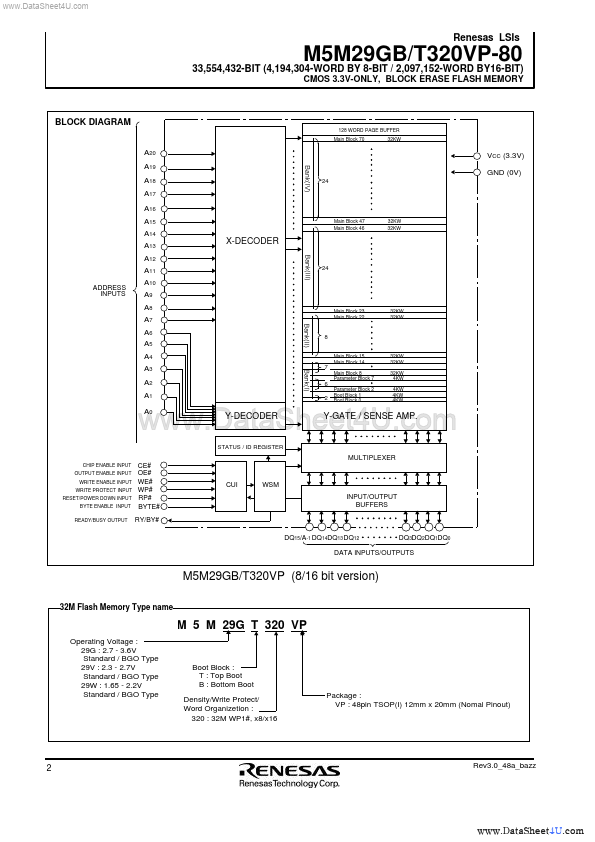

Renesas LSIs 33,554,432-BIT (4,194,304-WORD BY 8-BIT / 2,097,152-WORD BY16-BIT)

CMOS 3.3V-ONLY, BLOCK ERASE FLASH MEMORY DESCRIPTION

The Mobile FLASH M5M29GB/T320VP are 3.3V-only high speed 33,554,432-bit CMOS boot block Flash Memories with alternating BGO (Back Ground Operation) feature. The BGO feature of the device allows Program or Erase operations to be performed in one bank while the device simultaneously allows Read operations to be performed on the other bank. This BGO feature is suitable for mobile and personal puting, and munication products. The M5M29GB/T320VP are fabricated by CMOS technology for the peripheral circuits and DINOR(Divided bit line NOR)...