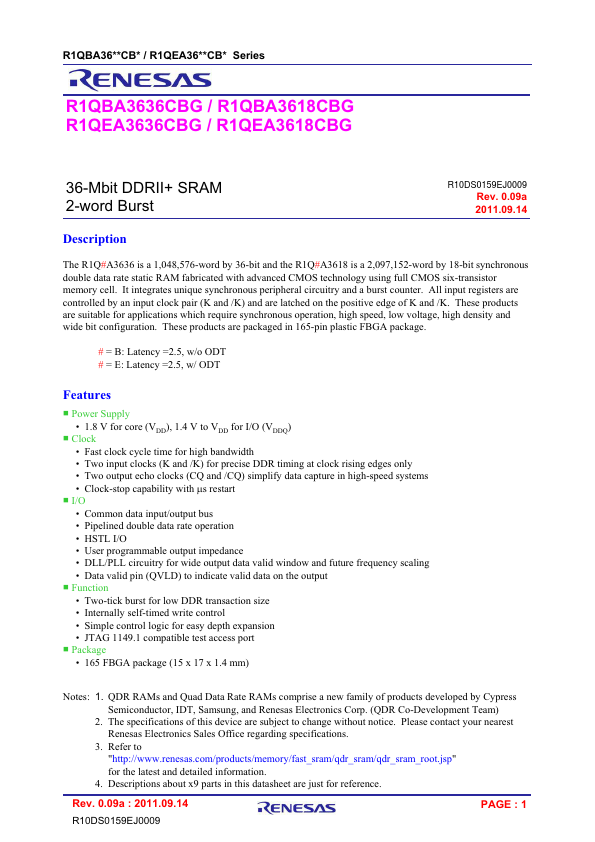

R1QBA3618CBG Overview

Description

The R1Q#A3636 is a 1,048,576-word by 36-bit and the R1Q#A3618 is a 2,097,152-word by 18-bit synchronous double data rate static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell. It integrates unique synchronous peripheral circuitry and a burst counter.

Key Features

- 1.8 V for core (VDD), 1.4 V to VDD for I/O (VDDQ) ႑ Clock

- Fast clock cycle time for high bandwidth

- Two input clocks (K and /K) for precise DDR timing at clock rising edges only

- Two output echo clocks (CQ and /CQ) simplify data capture in high-speed systems

- Clock-stop capability with Ps restart ႑ I/O

- Common data input/output bus

- Pipelined double data rate operation

- User programmable output impedance

- DLL/PLL circuitry for wide output data valid window and future frequency scaling

- Data valid pin (QVLD) to indicate valid data on the output ႑ Function