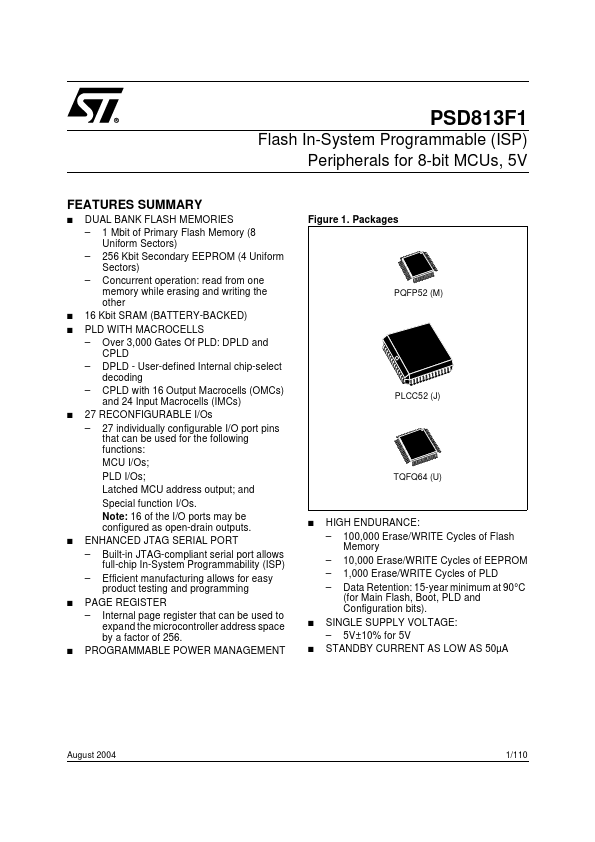

| Part | PSD813F1 |

|---|---|

| Description | Flash In-System Programmable Peripherals |

| Manufacturer | STMicroelectronics |

| Size | 638.67 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| Z-80A | Unknown Manufacturer | CPU Peripherals |

| PSD313-B-70J | STMicroelectronics | Low Cost Field Programmable Microcontroller Peripherals |

| PSD311R-B-70J | STMicroelectronics | Low Cost Field Programmable Microcontroller Peripherals |