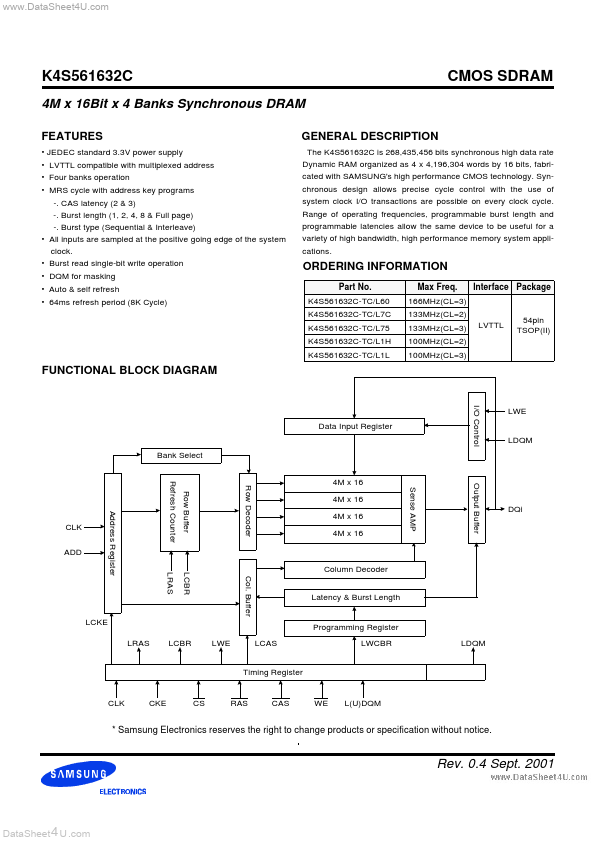

Datasheet Summary

..

CMOS SDRAM

256Mbit SDRAM

4M x 16bit x 4 Banks Synchronous DRAM LVTTL

Revision 0.4 Sept. 2001

- Samsung Electronics reserves the right to change products or specification without notice.

Rev. 0.4 Sept. 2001

DataSheet 4 U .

..

Revision History Revision 0.1 (Feb. 15, 2001)

- Added DC charcteristics.

CMOS SDRAM

Revision 0.2 (Mar. 06, 2001)

- Deleted "Preliminary"

- Changed DC charcteristics

Revision 0.3 (Jun 04, 2001)

- Corrected typo in DC characteristics

Revision 0.4 (Sep. 06, 2001)

- - Redefined IDD1 & IDD4 in DC Characteristics Changed the Notes in Operating AC Parameter. < Before > 5. For 1H/1L, tRDL=1CLK and...