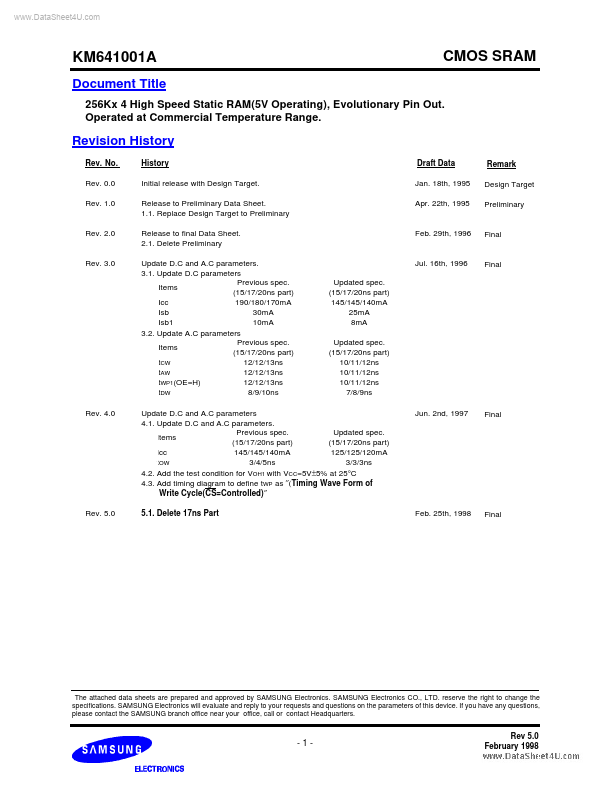

| Part | KM641001A |

|---|---|

| Description | CMOS SRAM |

| Manufacturer | Samsung Semiconductor |

| Size | 118.07 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| LH52256C-10LL | Sharp Corporation | 256K SRAM |

| 2114 | Fairchild Semiconductor | 1024 x 4 SRAM |

| HM628512 | Hitachi Semiconductor | 4 M SRAM (512-kword x 8-bit) |