TC518512FL-80DR

Overview

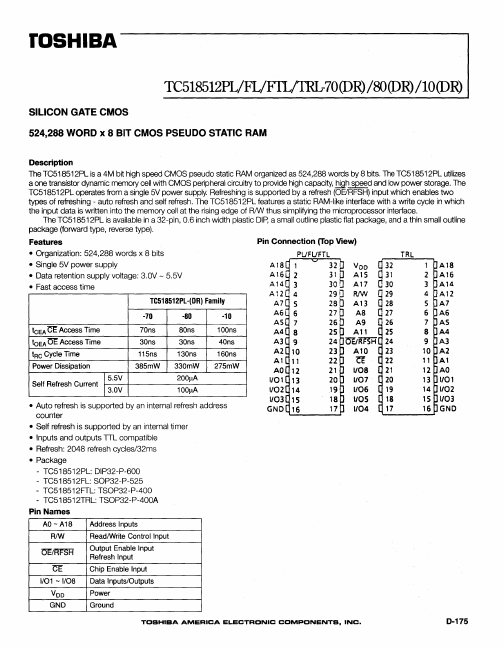

The TC518512PL is a 4M bit high speed CMOS pseudo static RAM organized as 524,288 words by 8 bits. The TC518512PL utilizes a one transistor dynamic memory cell with CMOS peripheral circuitry to provide high capacity, .!J!gh speed and low power storage.

- Organization: 524,288 words x 8 bits

- Single 5V p