Datasheet Summary

TOSHIBA

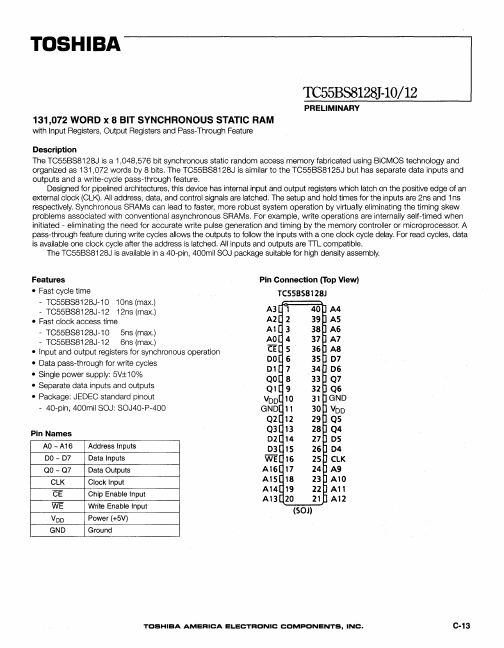

131,072 WORD x 8 BIT SYNCHRONOUS STATIC RAM with Input Registers, Output Registers and Pass-Through Feature

1l:55~128J-I0/12

PRELIMINARY

Description

The TC55BS8128J is a 1,048,576 bit synchronous static random access memory fabricated using BiCMOS technology and organized as 131,072 words by 8 bits. The TC55BS8128J is similar to the TC55BS8125J but has separate data inputs and outputs and a write-cycle pass-through feature.

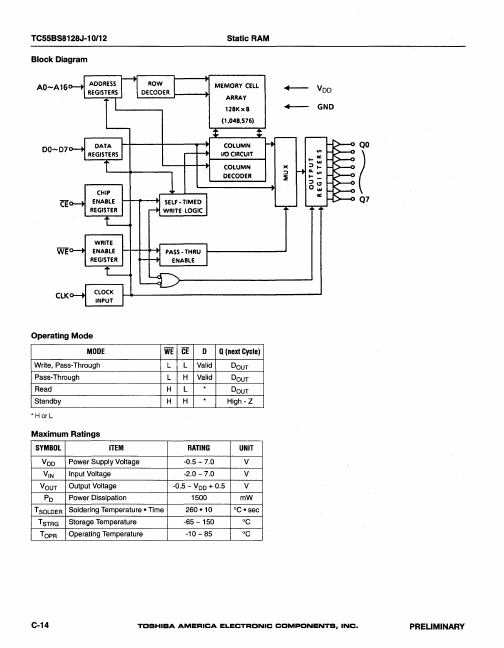

Designed for pipelined architectures, this device has internal input and output registers which latch on the positive edge of an external clock (ClK). All address; data, and control signals are latched. The setup and hold times for the inputs are 2ns and 1ns...