TC55V1864FT-10

Overview

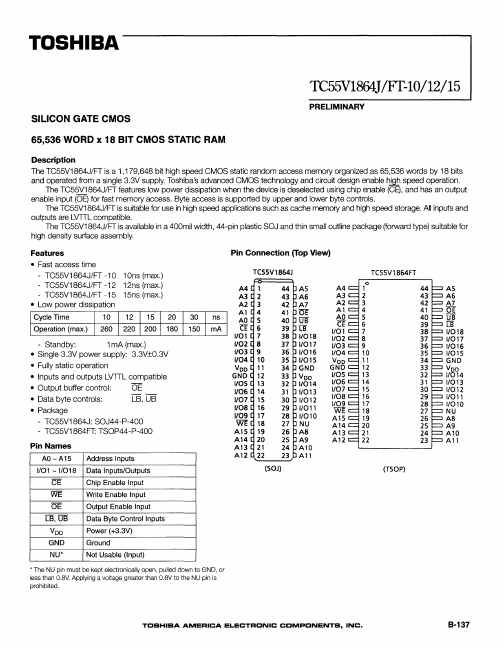

The TC55V1864J/FT is a 1,179,648 bit high speed CMOS static random access memory organized as 65,536 words by 18 bits and operated from a single 3.3V supply. Toshiba's advanced CMOS technology and circuit design enable hJ9!:l speed operation.

- Fast access time - TC55V1864J/FT -10 - TC55V1864J/FT -12 - TC55V1864J/FT -15

- Low pow