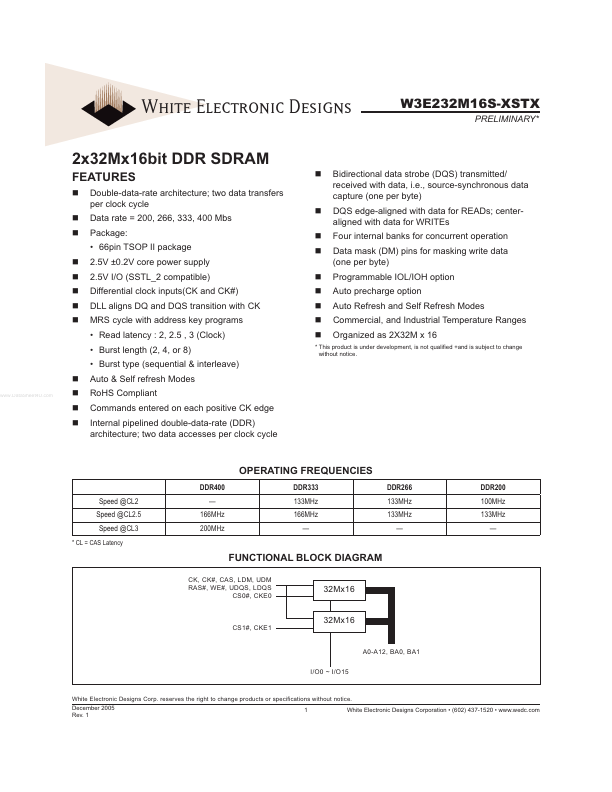

W3E232M16S-XSTX Description

White Electronic Designs 2x32Mx16bit DDR SDRAM.

W3E232M16S-XSTX Key Features

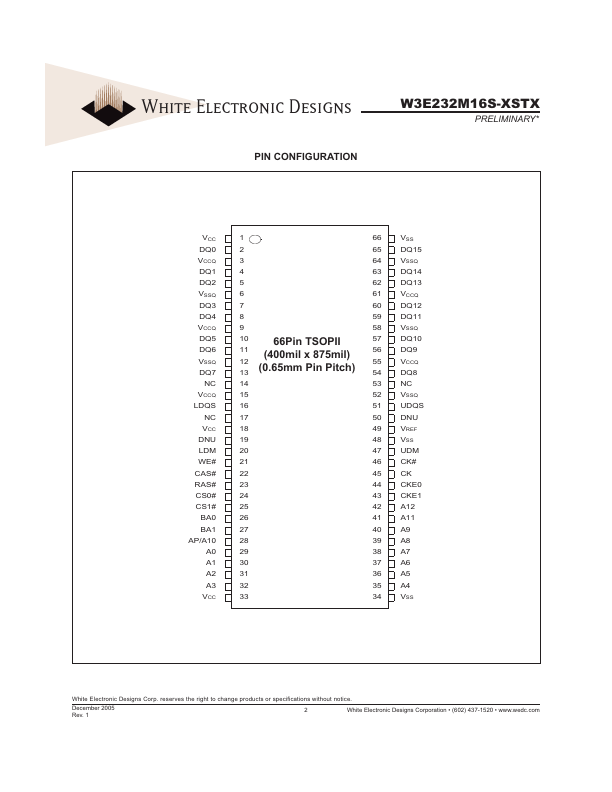

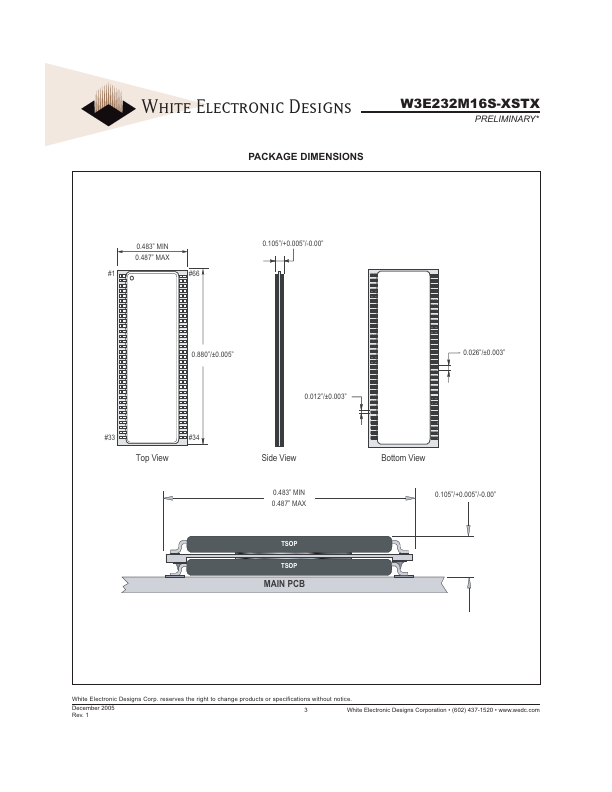

- 66pin TSOP II package 2.5V ±0.2V core power supply 2.5V I/O (SSTL_2 patible) Differential clock inputs(CK and CK#) DLL a

- Read latency : 2, 2.5 , 3 (Clock)

- Burst length (2, 4, or 8)

- Burst type (sequential & interleave) Auto & Self refresh Modes

- This product is under development, is not qualified +and is subject to change without notice

- CL = CAS Latency

- DDR266 133MHz 133MHz

- DDR200 100MHz 133MHz

- 166MHz 200MHz

- (602) 437-1520