XCR3512XL

Overview

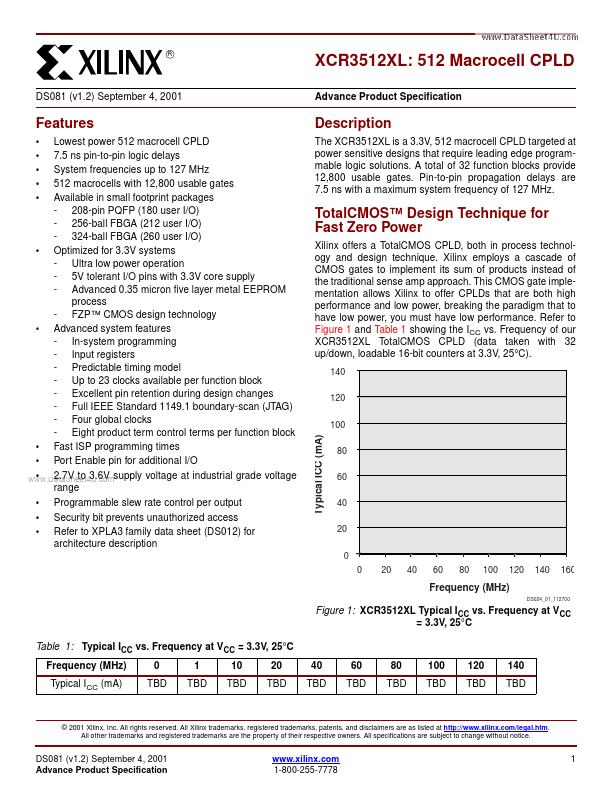

The XCR3512XL is a 3.3V, 512 macrocell CPLD targeted at power sensitive designs that require leading edge programmable logic solutions. A total of 32 function blocks provide 12,800 usable gates.

- Lowest power 512 macrocell CPLD 7.5 ns pin-to-pin logic delays System frequencies up to 127 MHz 512 macrocells with 12,800 usable gates Available in small footprint packages - 208-pin PQFP (180 user I/O) - 256-ball FBGA (212 user I/O) - 324-ball FBGA (260 user I/O) Optimized for 3.3V systems - Ultra low power operation - 5V tolerant I/O pins with 3.3V core supply - Advanced 0.35 micron five layer metal EEPROM process - FZP™ CMOS design technology Advanced system features - In-system programming - Input registers - Predictable timing model - Up to 23 clocks available per function block - Excellent pin retention during design changes - Full IEEE Standard 1149.1 boundary-scan (JTAG) - Four global clocks - Eight product term control terms per function block Fast ISP programming times Port Enable pin for additional I/O voltage at industrial grade voltage range