ZL30410 Overview

Description

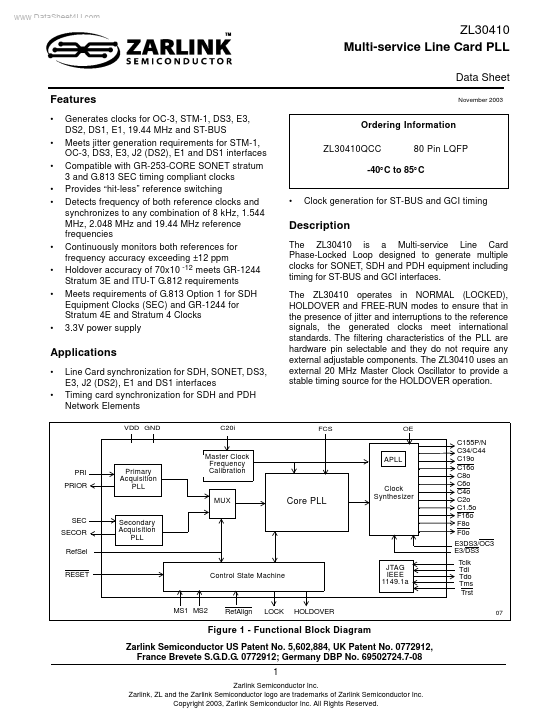

The ZL30410 is a Multi-service Line Card Phase-Locked Loop designed to generate multiple clocks for SONET, SDH and PDH equipment including timing for ST-BUS and GCI interfaces. The ZL30410 operates in NORMAL (LOCKED), HOLDOVER and FREE-RUN modes to ensure that in the presence of jitter and interruptions to the reference signals, the generated clocks meet international standards.

Key Features

- 40°C to 85° C

- Clock generation for ST-BUS and GCI timing