AT25XE011 Description

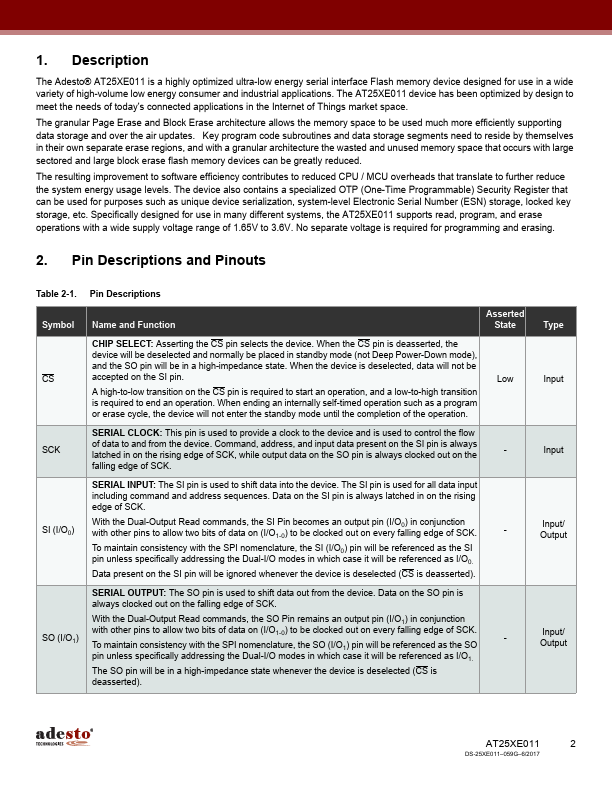

The Adesto® AT25XE011 is a highly optimized ultra-low energy serial interface Flash memory device designed for use in a wide variety of high-volume low energy consumer and industrial applications. The AT25XE011 device has been optimized by design to meet the needs of today's connected applications in the Internet of Things market space. The granular Page Erase and Block Erase architecture allows the memory space to...

AT25XE011 Key Features

- Single 1.65V

- 3.6V Supply

- Serial Peripheral Interface (SPI) patible

- Supports SPI Modes 0 and 3

- Supports Dual Output Read

- 104MHz Maximum Operating Frequency

- Clock-to-Output (tV) of 6 ns

- Flexible, Optimized Erase Architecture for Code + Data Storage