ADC3569 Overview

Key Specifications

Pins: 64

Height: 900 µm

Length: 9 mm

Width: 9 mm

Description

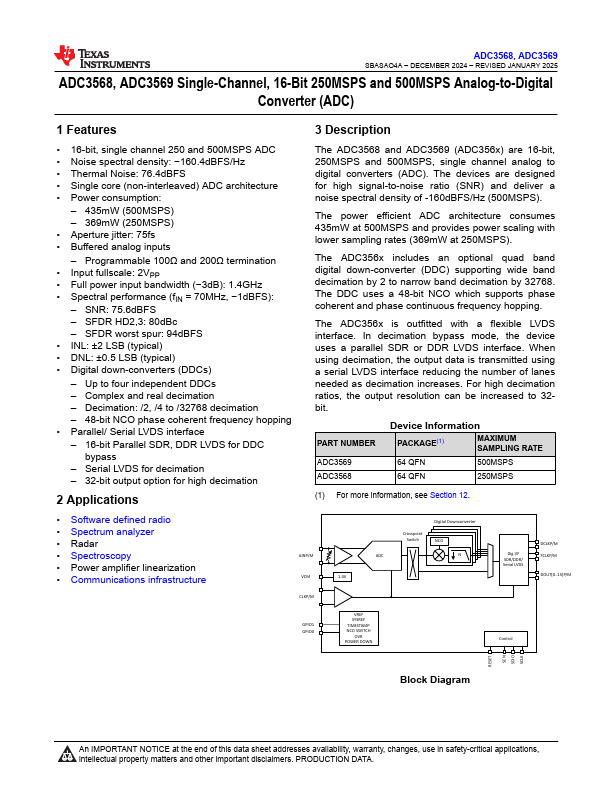

16-bit, single channel 250 and 500MSPS ADC - Noise spectral density: -160.4dBFS/Hz - Thermal Noise: 76.4dBFS - Single core (non-interleaved) ADC architecture - Power consumption: – 435mW (500MSPS) – 369mW (250MSPS) - Aperture jitter: 75fs - Buffered analog inputs – Programmable 100Ω and 200Ω termination - Input fullscale: 2VPP - Full power input bandwidth (-3dB): 1.4GHz - Spectral performance (fIN = 70MHz, -1dBFS): – SNR: 75.6dBFS – SFDR HD2,3: 80dBc – SFDR worst spur: 94dBFS - INL: ±2 LSB (typical) - DNL: ±0.5 LSB (typical) - Digital down-converters (DDCs) – Up to four independent DDCs – Complex and real decimation – Decimation: /2, /4 to /32768 decimation – 48-bit NCO phase coherent frequency hopping - Parallel/ Serial LVDS interface – 16-bit Parallel SDR, DDR LVDS for DDC bypass – Serial LVDS for decimation – 32-bit output option for high decimation.