ADS6425 Overview

Key Specifications

Package: VQFN

Mount Type: Surface Mount

Pins: 64

Operating Voltage: 3.3 V

Description

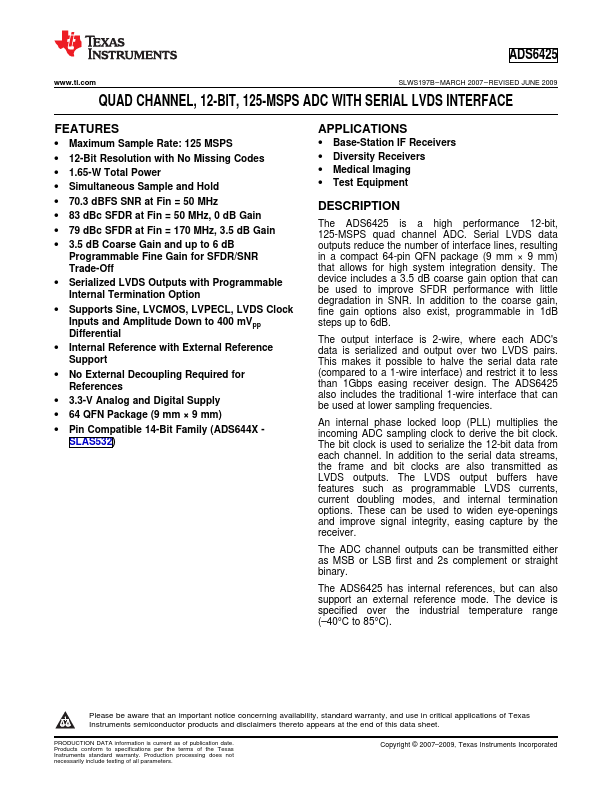

The ADS6425 is a high performance 12-bit, 125-MSPS quad channel ADC. Serial LVDS data outputs reduce the number of interface lines, resulting in a compact 64-pin QFN package (9 mm × 9 mm) that allows for high system integration density.

Key Features

- Maximum Sample Rate: 125 MSPS

- 12-Bit Resolution with No Missing Codes

- 1.65-W Total Power

- Simultaneous Sample and Hold

- 70.3 dBFS SNR at Fin = 50 MHz

- 83 dBc SFDR at Fin = 50 MHz, 0 dB Gain

- 79 dBc SFDR at Fin = 170 MHz, 3.5 dB Gain

- 3.5 dB Coarse Gain and up to 6 dB Programmable Fine Gain for SFDR/SNR Trade-Off

- Serialized LVDS Outputs with Programmable Internal Termination Option

- Supports Sine, LVCMOS, LVPECL, LVDS Clock Inputs and Amplitude Down to 400 mVpp Differential