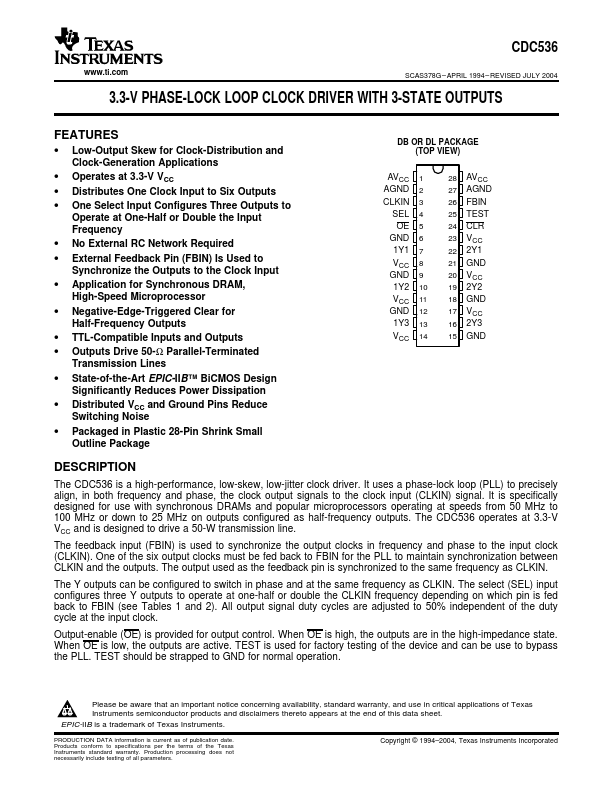

Datasheet Summary

.ti.

SCAS378G

- APRIL 1994

- REVISED JULY 2004

3.3-V PHASE-LOCK LOOP CLOCK DRIVER WITH 3-STATE OUTPUTS

Features

- Low-Output Skew for Clock-Distribution and Clock-Generation Applications

- Operates at 3.3-V VCC

- Distributes One Clock Input to Six Outputs

- One Select Input Configures Three Outputs to

Operate at One-Half or Double the Input Frequency

- No External RC Network Required

- External Feedback Pin (FBIN) Is Used to

Synchronize the Outputs to the Clock Input

- Application for Synchronous DRAM, High-Speed Microprocessor

- Negative-Edge-Triggered Clear for Half-Frequency Outputs

- TTL-patible Inputs and Outputs

- Outputs Drive 50-Ω Parallel-Terminated

Transmission...