Datasheet Summary

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

SNAS597C

- JULY 2012

- REVISED JANUARY 2016

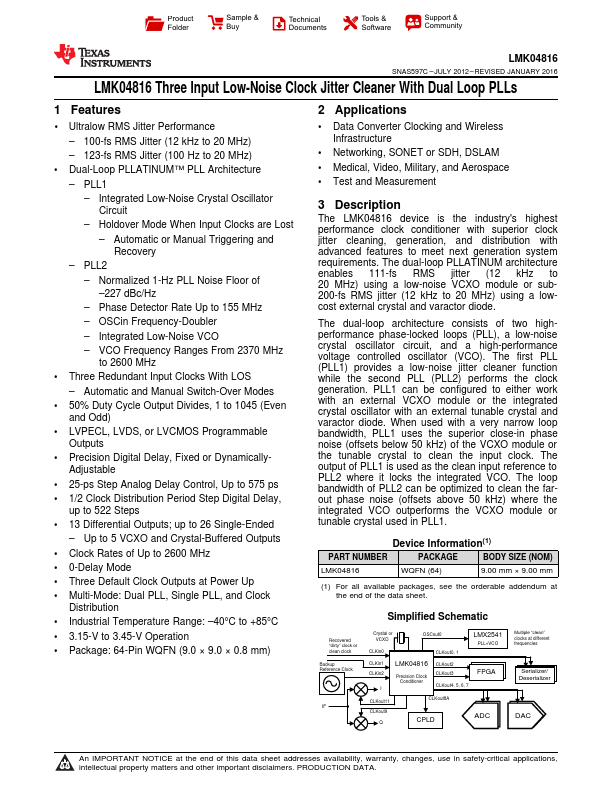

LMK04816 Three Input Low-Noise Clock Jitter Cleaner With Dual Loop PLLs

1 Features

- 1 Ultralow RMS Jitter Performance

- 100-fs RMS Jitter (12 kHz to 20 MHz)

- 123-fs RMS Jitter (100 Hz to 20 MHz)

- Dual-Loop PLLATINUM™ PLL Architecture

- PLL1

- Integrated Low-Noise Crystal Oscillator Circuit

- Holdover Mode When Input Clocks are Lost

- Automatic or Manual Triggering and Recovery

- PLL2

- Normalized 1-Hz PLL Noise Floor of

- 227 dBc/Hz

- Phase Detector Rate Up to 155 MHz

- OSCin Frequency-Doubler

- Integrated Low-Noise VCO

- VCO Frequency Ranges From...