LMK5C33216

Overview

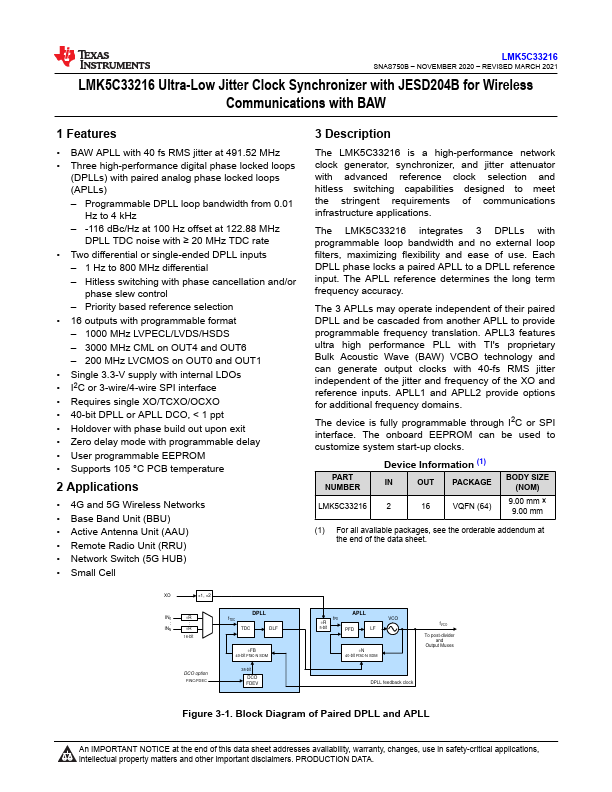

The LMK5C33216 is a high-performance network clock generator, synchronizer, and jitter attenuator with advanced reference clock selection and hitless switching capabilities designed to meet the stringent requirements of communications infrastructure applications. The LMK5C33216 integrates 3 DPLLs with programmable loop bandwidth and no external loop filters, maximizing flexibility and ease of use.

- BAW APLL with 40 fs RMS jitter at 491.52 MHz

- Three high-performance digital phase locked loops (DPLLs) with paired analog phase locked loops (APLLs) - Programmable DPLL loop bandwidth from 0.01 Hz to 4 kHz - -116 dBc/Hz at 100 Hz offset at 122.88 MHz