LMK5B12204

LMK5B12204 is Ultra-Low Jitter Network Synchronizer Clock manufactured by Texas Instruments.

.ti.

LMK5B12204 SNAS810A

- MAY 2020

- REVISEDLMJAKNU5ABR1Y22200241

SNAS810A

- MAY 2020

- REVISED JANUARY 2021

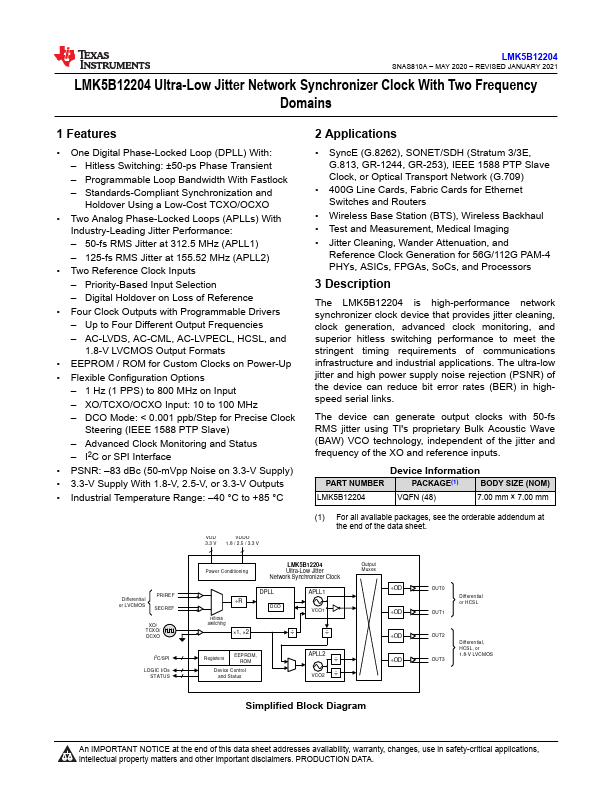

LMK5B12204 Ultra-Low Jitter Network Synchronizer Clock With Two Frequency

Domains

1 Features

- One Digital Phase-Locked Loop (DPLL) With:

- Hitless Switching: ±50-ps Phase Transient

- Programmable Loop Bandwidth With Fastlock

- Standards-pliant Synchronization and Holdover Using a Low-Cost TCXO/OCXO

- Two Analog Phase-Locked Loops (APLLs) With Industry-Leading Jitter Performance:

- 50-fs RMS Jitter at 312.5 MHz (APLL1)

- 125-fs RMS Jitter at 155.52 MHz (APLL2)

- Two Reference Clock Inputs

- Priority-Based Input Selection

- Digital Holdover on Loss of Reference

- Four...