LMK5C33216

LMK5C33216 is Ultra-Low Jitter Clock Synchronizer manufactured by Texas Instruments.

.ti.

LMK5C33216 SNAS750B

- NOVEMBER 2020

- REVISLEMD MKA5RCC3H32201261

SNAS750B

- NOVEMBER 2020

- REVISED MARCH 2021

LMK5C33216 Ultra-Low Jitter Clock Synchronizer with JESD204B for Wireless munications with BAW

1 Features

- BAW APLL with 40 fs RMS jitter at 491.52 MHz

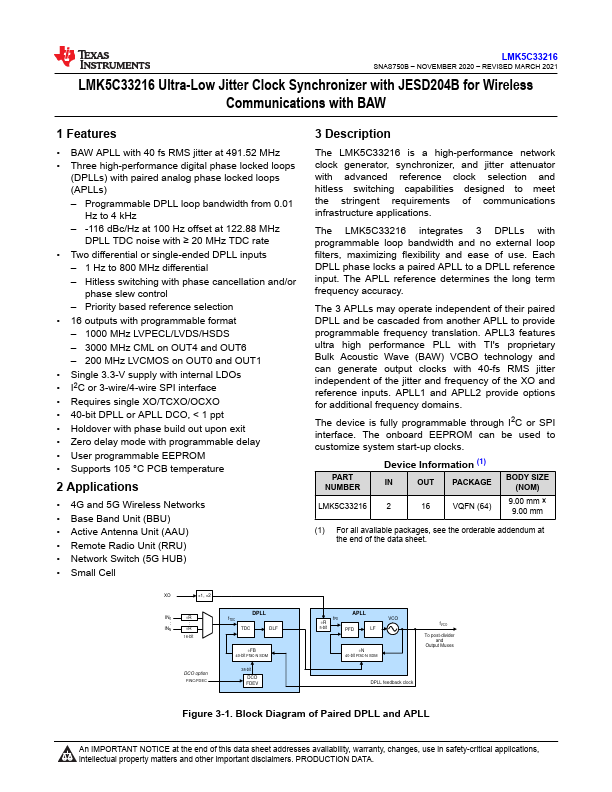

- Three high-performance digital phase locked loops

(DPLLs) with paired analog phase locked loops (APLLs)

- Programmable DPLL loop bandwidth from 0.01

Hz to 4 kHz

- -116 dBc/Hz at 100 Hz offset at 122.88 MHz

DPLL TDC noise with ≥ 20 MHz TDC rate

- Two differential or single-ended DPLL inputs

- 1 Hz to 800 MHz differential

- Hitless switching with phase cancellation and/or phase slew control

- Priority based...