LMK5B33414 Key Features

- Ultra-low jitter BAW VCO based Ethernet clocks

- 42-fs typical/ 60-fs maximum RMS jitter at 312.5 MHz

- 47-fs typical/ 65-fs maximum RMS jitter at 156.25 MHz

- 3 high-performance Digital Phase Locked Loops (DPLLs) with paired Analog Phase Locked Loops (APLLs)

- Programmable DPLL loop bandwidth from 1 mHz to 4 kHz

- < 1-ppt DCO frequency adjustment step size

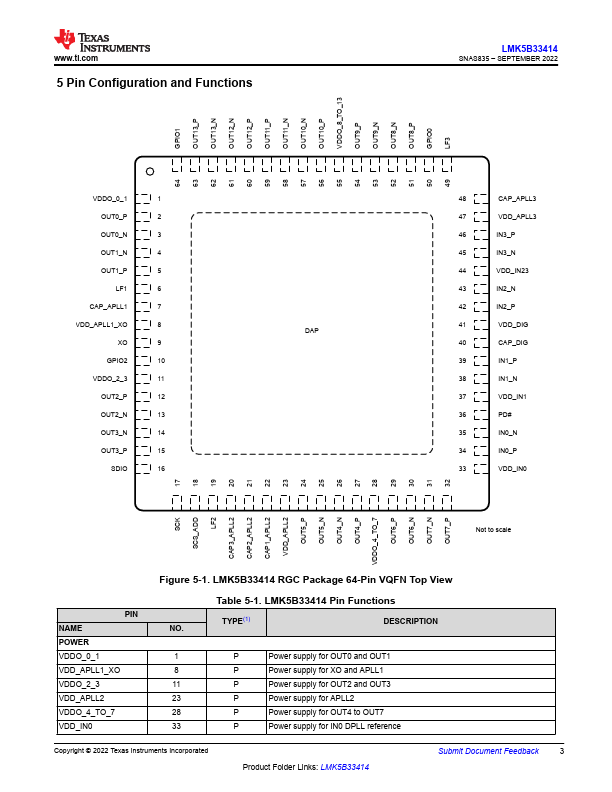

- 4 differential or single-ended DPLL inputs

- 1-Hz (1-PPS) to 800-MHz input frequency

- Digital holdover and hitless switching

- 14 differential outputs with programmable HSDS/ LVPECL, LVDS and HSCL output formats