PLL1707-Q1

Description

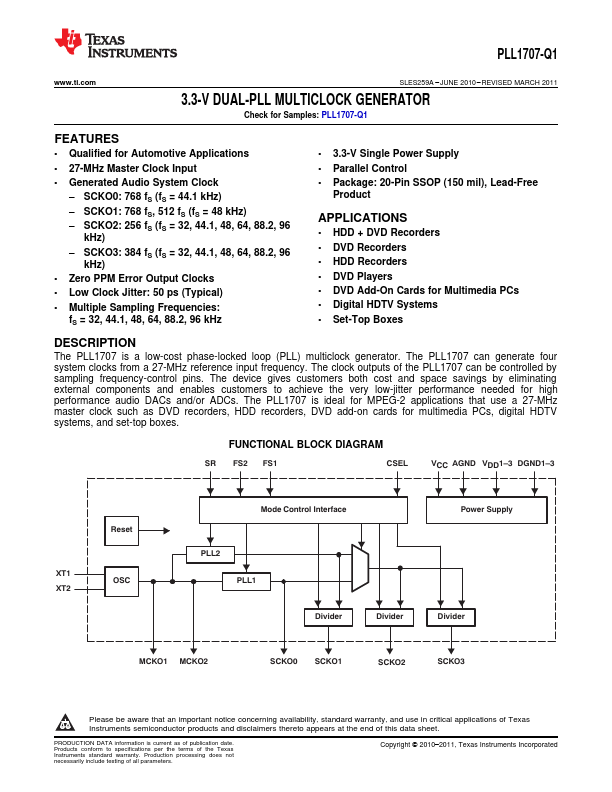

The PLL1707 is a low-cost phase-locked loop (PLL) multiclock generator.

Key Features

- Qualified for Automotive Applications

- 27-MHz Master Clock Input

- Generated Audio System Clock

- Zero PPM Error Output Clocks

- Low Clock Jitter: 50 ps (Typical)

- Multiple Sampling Frequencies

- 3.3-V Single Power Supply

- Parallel Control

- Package: 20-Pin SSOP (150 mil), Lead-Free

Applications

- HDD + DVD Recorders